With AMD’s Zen 5 CPU structure solely a month away from its first product releases, the brand new CPU structure was positioned entrance and heart for AMD’s prime Computex 2024 keynote. Outlining how Zen 5 will result in improved merchandise throughout AMD’s complete portfolio, the corporate laid out their product plans for the total triad: cellular, desktop, and servers. And whereas server chips would be the final components to be launched, AMD additionally saved the most effective for final by showcasing a 192 core EPYC “Turin” chip.

Turin is the catch-all codename for AMD’s Zen 5-based EPYC server processors – what’s going to presumably be the EPYC 9005 sequence. The firm has beforehand disclosed the title in earnings calls and different investor capabilities, outlining that the chip was already sampling to clients and that the silicon was “trying nice.”

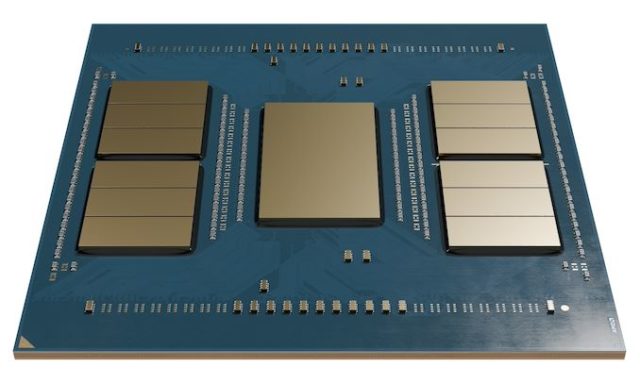

The Computex reveal, in flip, is the primary time that the silicon has been proven off to the general public. And with it, we’ve obtained the primary official affirmation of the chip’s specs. With SKUs as much as 192 CPU cores, it’s going to be a monster of an x86 CPU.

| AMD EPYC CPU Generations | ||||

| AnandTech | EPYC fifth Gen (Turin, Z5c) |

EPYC 9704 (Bergamo) |

EPYC 9004 (Genoa) |

EPYC 7003 (Milan) |

| CPU Architecture | Zen 5c | Zen 4c | Zen 4 | Zen 3 |

| Max CPU Cores | 192 | 128 | 96 | 64 |

| Memory Channels | 12 x DDR5 | 12 x DDR5 | 12 x DDR5 | eight x DDR4 |

| PCIe Lanes | 128 x 5.0 | 128 x 5.0 | 128 x 5.0 | 128 x 4.0 |

| L3 Cache | ? | 256MB | 384MB | 256MB |

| Max TDP | 360W? | 360W | 400W | 280W |

| Socket | SP5 | SP5 | SP5 | SP3 |

| Manufacturing Process |

CCD: TSMC N3 IOD:TSMC N6 |

CCD: TSMC N5 IOD: TSMC N6 |

CCD: TSMC N5 IOD: TSMC N6 |

CCD: TSMC N7 IOD: GloFo 14nm |

| Release Date | H2'2024 | 06/2023 | 11/2022 | 03/2021 |

Though solely a short tease, AMD’s Turin showcase did affirm a number of, long-suspected particulars in regards to the platform. AMD will as soon as once more be utilizing their socket SP5 platform for Turin processors, which implies the chips are drop-in suitable with EPYC 9004 Genoa (and Bergamo). The reuse of SP5 signifies that clients and server distributors can instantly swap out chips with out having to construct/deploy complete new programs. It additionally signifies that Turin may have the identical base reminiscence and I/O choices because the EPYC 9004 sequence: 12 channels of DDR5 reminiscence, and 128 PCIe 5.Zero lanes.

In phrases of energy consumption, current SP5 processors high out at 400 Watts, and we’d anticipate the identical for these new, socket-compatible chips.

As for the Turin chip itself, whereas AMD isn’t going into additional element on its configuration, all indicators level to this being a Zen 5c configuration – that’s, constructed utilizing CCDs designed round AMD’s compact Zen 5 core configuration. This would make the Turin chip on show the successor to Bergamo (EPYC 9704), which was AMD’s first compact core server processor, utilizing Zen 4c cores. AMD’s compact CPU cores usually commerce off per-core efficiency in favor of permitting extra CPU cores total, with decrease clockspeed limits (by design) and fewer cache reminiscence all through the chip.

According to AMD, the CCDs on this chip have been fabbed on a 3nm course of (undoubtedly TSMC’s), with AMD apparently seeking to benefit from the densest course of obtainable with a view to maximize the variety of CPU cores the can place on a single chip. Even then, the CCDs featured listed here are fairly sizable, and whereas we’re ready for official die dimension numbers, it could come as no shock if Zen 5’s larger transistor rely greater than offset the area financial savings of transferring to 3nm. Still, AMD has been in a position to squeeze 12 CCDs on to the chip – Four extra…