For TSMC, being the world’s largest foundry with almost 500 prospects has its peculiarities. On the one hand, the corporate can serve nearly any shopper with nearly any necessities. On the opposite hand, it has to remain forward of everybody else each by way of capability and by way of know-how. As far as capability is worried, TSMC is unchallenged and isn’t going to be for years to return. As for fabrication applied sciences, TSMC has not too long ago reiterated that it is assured that its N2, N3, and N4 processes might be out there on time and might be extra superior than competing nodes.

Confidence

Early this yr TSMC considerably boosted its 2021 CapEx price range to a $25 – $28 billion vary, additional rising it to round $30 billion as part of its three-year plan to spend $100 billion on manufacturing capacities and R&D.

About 80% of TSMC’s $30 billion capital price range this yr might be spent on increasing capacities for superior applied sciences, comparable to 3nm, 4nm/5nm, and 6nm/7nm. Analysts from China Renaissance Securities consider that many of the cash on superior nodes might be used to develop TSMC’s N5 capability to 110,000 ~ 120,000 wafer begins per 30 days (WSPM) by the top of the yr. Meanwhile, TSMC stated that 10% of its CapEx might be allotted for superior packaging and masks making, whereas one other 10% might be spent on specialty applied sciences (which incorporates tailor-made variations of mature nodes).

TMSC’s the latest CapEx hikes bulletins had been made after Intel introduced its IDM 2.Zero technique (that entails in-house manufacturing, outsourcing, and foundry operations) and to a big diploma reaffirms TMSC’s confidence in each short-term and long-term future even forward of intensified competitors.

“As a leading pure-play foundry, TSMC has never been short on competition in our 30-plus-year history, yet we know how to compete,” stated C.C. Wei, president and CEO of TSMC, at a current convention name with analysts and traders. “We will continue to focus on delivering technology leadership, manufacturing excellence, and earning our customers’ trust. The last point, customers’ trust, is fairly important because we do not have internal products that compete with customer.”

| Advertised PPA Improvements of New Process Technologies Data introduced throughout convention calls, occasions, press briefings and press releases |

|||||||||

| TSMC | |||||||||

| N7 vs 16FF+ |

N7 vs N10 |

N7P vs N7 |

N7+ vs N7 |

N5 vs N7 |

N5P vs N5 |

N4 vs N5 |

N3 vs N5 |

||

| Power | -60% | <-40% | -10% | -15% | -30% | -10% | decrease | -25-30% | |

| Performance | +30% | ? | +7% | +10% | +15% | +5% | larger | +10-15% | |

| Logic Area

Reduction % (Density) |

70% |

>37% |

– |

~17% |

0.55x

-45% (1.8x) |

– |

? | 0.58x

-42% (1.7x) |

|

| Volume Manufacturing |

2018 | 2018 |

2019 | Q2 2019 |

Q2 2020 | 2021 | 2022 | H2 2022 | |

N5 Gaining Customers

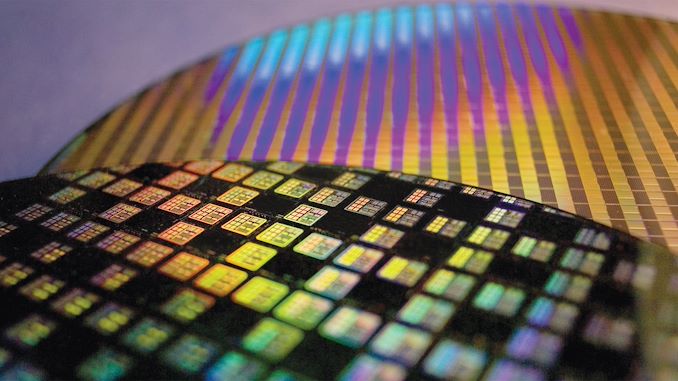

TSMC was the primary firm to start out excessive quantity manufacturing (HVM) of chips utilizing its N5 (5 nm) course of know-how in mid-2020.

Initially, the node was used solely for TSMC’s alpha prospects — Apple and HiSilicon. Shipments to the latter ceased on September 14, which left the entire modern capability to Apple. By now, extra prospects are prepared with their N5 designs, so the adoption of this node is rising. Meanwhile, TSMC says extra prospects are planning to make use of N5 household of applied sciences (together with N5, N5P, and N4) than it anticipated simply a number of months in the past.

“N5 is already in its second year of volume production with yield better than our original plan,” stated Mr. Wei. N5 demand continues to be robust, pushed by smartphone and HPC purposes, and we anticipate N5 to contribute round 20% of our wafer income in…

![[Video] Discover Your Ideal Bespoke AI Laundry Appliance](https://loginby.com/itnews/wp-content/uploads/2026/04/Video-Discover-Your-Ideal-Bespoke-AI-Laundry-Appliance-100x75.jpg)