Following a relative lull within the desktop reminiscence business within the earlier decade, the previous few years have seen a flurry of recent reminiscence requirements and kind elements enter improvement. Joining the standard DIMM/SO-DIMM kind elements, we have seen the introduction of space-efficient DDR5 CAMM2s, their LPDDR5-based counterpart the LPCAMM2, and the high-clockspeed optimized CUDIMM. But JEDEC, the business group behind these efforts, isn’t carried out there. In a press launch despatched out initially of the week, the group introduced that it’s engaged on requirements for DDR5 Multiplexed Rank DIMMs (MRDIMM) for servers, in addition to an up to date LPCAMM customary to go along with next-generation LPDDR6 reminiscence.

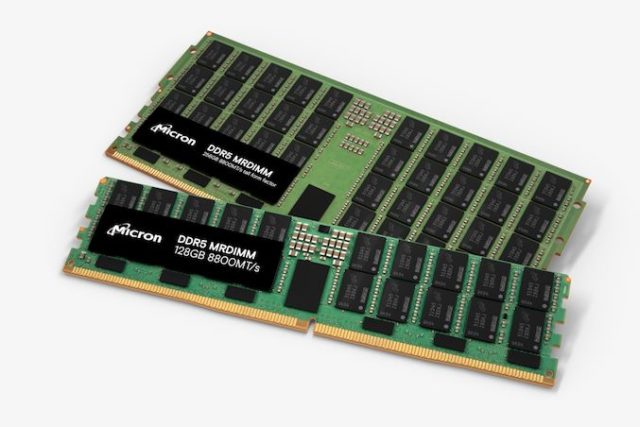

Just final week Micron launched the business’s first DDR5 MRDIMMs, that are timed to launch alongside Intel’s Xeon 6 server platforms. But whereas Intel and its companions are transferring full steam forward on MRDIMMs, the MRDIMM specification has not been totally ratified by JEDEC itself. All instructed, it is commonplace to see Intel pushing the envelope right here on new reminiscence applied sciences (the corporate is sufficiently big to bootstrap its personal ecosystem). But as MRDIMMs are in the end meant to be greater than only a instrument for Intel, a correct business customary remains to be wanted – even when that takes a bit longer.

Under the hood, MRDIMMs proceed to make use of DDR5 elements, form-factor, pinout, SPD, energy administration ICs (PMICs), and thermal sensors. The main change with the know-how is the introduction of multiplexing, which mixes a number of knowledge alerts over a single channel. The MRDIMM customary additionally provides RCD/DB logic in a bid to spice up efficiency, improve capability of reminiscence modules as much as 256 GB (for now), shrink latencies, and scale back energy consumption of high-end reminiscence subsystems. And, maybe key to MRDIMM adoption, the usual is being applied as a backwards-compatible extension to conventional DDR5 RDIMMs, that means that MRDIMM-capable servers can use both RDIMMs or MRDIMMs, relying on how the operator opts to configure the system.

The MRDIMM customary goals to double the height bandwidth to 12.8 Gbps, rising pin velocity and supporting greater than two ranks. Additionally, a “Tall MRDIMM” kind issue is within the works (and pictured above), which is designed to permit for larger capability DIMMs by offering extra space for laying down reminiscence chips. Currently, extremely excessive capability DIMMs require utilizing costly, multi-layer DRAM packages that use through-silicon vias (3DS packaging) to connect the person DRAM dies; a Tall MRDIMM, then again, can simply use a bigger variety of commodity DRAM chips. Overall, the Tall MRDIMM kind issue allows twice the variety of DRAM single-die packages on the DIMM.

Meanwhile, this week’s announcement from JEDEC gives the primary important perception into what to anticipate from LPDDR6 CAMMs. And regardless of LPDDR5 CAMMs having barely made it out the door, some important shifts with LPDDR6 itself implies that JEDEC might want to make some main modifications to the CAMM customary to accommodate the newer reminiscence kind.

JEDEC Presentation: The CAMM2 Journey and Future Potential

Besides the upper reminiscence clockspeeds allowed by LPDDR6 – JEDEC is concentrating on knowledge switch charges of 14.four GT/s and better – the brand new reminiscence form-factor will even incorporate an altogether new connector array. This is to accommodate LPDDR6’s wider reminiscence bus, which sees the channel width of a person reminiscence chip develop from 16-bits broad to 24-bits broad. As a end result, the present LPCAMM design, which is meant to match the PC customary of a cumulative 128-bit (16×8) design must be reconfigured to match LPDDR6’s alterations.

Ultimately, JEDEC is concentrating on a 24-bit subhannel/48-bit channel design, which can lead to a 192-bit broad LPCAMM. While the LPCAMM…

![[Video] Discover Your Ideal Bespoke AI Laundry Appliance](https://loginby.com/itnews/wp-content/uploads/2026/04/Video-Discover-Your-Ideal-Bespoke-AI-Laundry-Appliance-100x75.jpg)