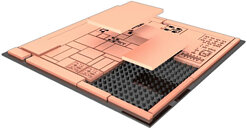

This might give AMD a modular manner so as to add machine-learning capabilities to a number of of their designs by means of the inclusion of such a chiplet, and is perhaps AMD’s manner of reaching {hardware} acceleration of a DLSS-like characteristic. This would keep away from the shortcomings related to implementing it within the GPU package deal itself – a rise in general die space, with thus elevated value and diminished yields, whereas on the similar time enabling AMD to deploy it in different merchandise apart from GPU packages. The patent describes the potential of totally different manufacturing applied sciences being employed within the chiplet-based design – harkening again to the I/O modules in Ryzen CPUs, manufactured through a 12 nm course of, and never the 7 nm one used for the core chiplets. The patent additionally describes acceleration of cache-requests from the GPU die to the cache chiplet, and on-the-fly utilization of it as precise cache, or as directly-addressable reminiscence.

![[Interview] ‘Bixby Will Be Your Go-To Starting Point for](https://loginby.com/itnews/wp-content/uploads/2026/04/1775675971_Interview-‘Bixby-Will-Be-Your-Go-To-Starting-Point-for-100x75.jpg)