The annual IEEE International Solid-State Circuits Conference covers a variety of subjects of curiosity to AnandTech. Every yr the convention features a session on non-volatile recollections the place many of the NAND flash reminiscence producers share technical particulars of their newest developments. At the convention we get extra data than these corporations are normally prepared to share in press briefings, and the shows are normally about know-how that might be hitting the market throughout the coming yr.

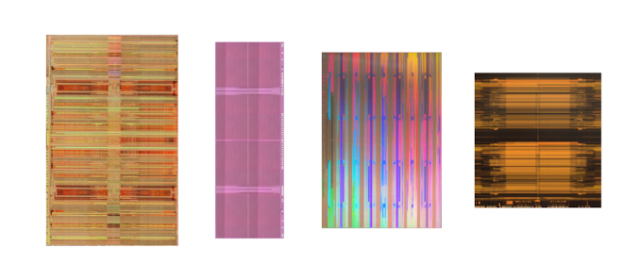

At ISSCC 2021 this week, 4 of the six main 3D NAND flash reminiscence producers are presenting their latest 3D NAND know-how. Samsung, SK hynix and Kioxia (+Western Digital) are sharing their newest 3D TLC NAND designs and Intel is presenting their 144-layer 3D QLC NAND. Not taking part this yr are Micron (who introduced their 176L 3D NAND late final yr) and Chinese newcomer YMTC.

3D TLC (3-bit per cell) Updates

Samsung, SK hynix, and Kioxia/WD introduced details about their upcoming generations of 3D TLC. Not proven right here is Micron's 176L TLC, as a result of they haven't launched most of this information for his or her newest era of 3D NAND.

| 3D TLC NAND Flash Memory ISSCC Presentations |

||||||

| Samsung | SK hynix | Kioxia (Toshiba) WD |

||||

| Year Presented at ISSCC | 2021 | 2019 | 2021 | 2021 | 2019 | 2018 |

| Layers | 128 | 176 | >170 | 128 | 96 | |

| Die Capacity | 512 Gb | 512 Gb | 512 Gb | 1 Tb | 512 Gb | 512 Gb |

| Die Size (mm2) | 101.58 | 98 | 66 | 86 | ||

| Density (Gbit/mm2) | 8.5 | 5 | 10.8 | 10.4 | 7.8 | 5.95 |

| IO Speed | 2.0 Gb/s | 1.2 Gb/s | 1.6 Gb/s | 2.0 Gb/s | 1.066 Gb/s | 533 Mb/s |

| Program Throughput | 184 MB/s | 82 MB/s | 168 MB/s | 160 MB/s | 132 MB/s | 57 MB/s |

| Read Latency (tR) | 40 µs | 45 µs | 50 µs | 50 µs | 56 µs | 58 µs |

| Erase Block Size | 24 MB | 18 MB | ||||

| Planes | 4? | 2 | 4 | 4 | 4 | 2 |

| CuA / PuC | Yes | No | Yes | Yes | Yes | No |

Unsurprisingly, it appears doubtless that Samsung will once more be within the lead for efficiency, with the bottom learn latency and quickest write speeds. However, their bit density remains to be clearly lagging despite the fact that they're claiming a 70% leap with this era. In the previous, their lagging density hasn't been as a lot of a draw back as it’d seem at first look, as a result of Samsung has been capable of keep away from utilizing string stacking and may manufacture a stack of 128 layers as a single deck whereas their rivals have all needed to cut up their stack into two decks, rising the variety of fab steps required. This could be the era that brings Samsung's inevitable adoption of string stacking, but when that's the case then their lingering density drawback is reasonably disappointing. On the opposite hand, in the event that they've managed to place off that transition for yet one more era and achieved this type of density enhance solely utilizing a mixture of different methods (most notably a CMOS beneath Array format), then it's a really spectacular advance and it could be protected to say that Samsung is years forward of the competitors relating to the excessive facet ratio etching of the vertical channels that’s the most important fab step in scaling 3D NAND. We'll know extra as soon as Samsung discloses the precise layer rely, however they're conserving that secret for now—which hints that they don't anticipate to have the best layer rely to brag about.

The TLC elements described by SK hynix and Kioxia/WD look pretty comparable, save for the large distinction that SK hynix is speaking a couple of 512Gb die and Kioxia is speaking a couple of…