Today Xilinx is saying an growth to its Versal household, centered particularly on low energy and edge gadgets. Xilinx Versal is the productization of a mix of many various processor applied sciences: programmable logic gates (FPGAs), Arm cores, quick reminiscence, AI engines, programmable DSPs, hardened reminiscence controllers, and IO – the advantages of all these applied sciences implies that Versal can scale from the excessive finish Premium (launched in 2020), and now right down to edge-class gadgets, all constructed on TSMC’s 7nm processes. Xilinx’s new Versal AI Edge processors begin at 6 W, all the way in which as much as 75 W.

Going for the ACAP

A few years in the past, Xilinx noticed a change in its buyer necessities – regardless of being an FPGA vendor, clients wished one thing extra akin to an everyday processor, however with the flexibleness with an FPGA. In 2018, the corporate launched the idea of an ACAP, an Adaptive Computing Acceleration Platform that supplied hardened compute, reminiscence, and IO like a standard processor, but additionally substantial programmable logic and acceleration engines from an FPGA. The first high-end ACAP processors, constructed on TSMC N7, have been showcased in 2020 and featured massive premium silicon, some with HBM, for top efficiency workloads.

So slightly than having a design that was 100% FPGA, by transferring a few of that die space to hardened logic like processor cores or reminiscence, Xilinx’s ACAP design permits for a full vary of devoted standardized IP blocks at decrease energy and smaller die space, whereas nonetheless retaining a superb portion of the silicon for FPGA permitting clients to deploy customized logic options. This has been vital within the development of AI, as algorithms are evolving, new frameworks are taking form, or totally different compute networks require totally different balances of assets. Having an FPGA on die, coupled with customary hardened IP, permits a single product set up to final for a few years as algorithms rebalance and get up to date.

Xilinx Versal AI Edge: Next Generation

On that closing level about having an put in product for a decade and having to replace the algorithms, in no space is that extra true than with conventional ‘edge’ gadgets. At the ‘edge’, we’re speaking sensors, cameras, industrial methods, business methods – gear that has to final over its lengthy set up lifetime with no matter {hardware} it has in it. There are edge methods at the moment constructed on pre-2000 {hardware}, to provide you a scope of this market. As a outcome, there may be all the time a push to make edge gear extra malleable as wants and use instances change. This is what Xilinx is focusing on with its new Versal AI Edge portfolio – the flexibility to repeatedly replace ‘smart’ performance in gear reminiscent of cameras, robotics, automation, medical, and different markets.

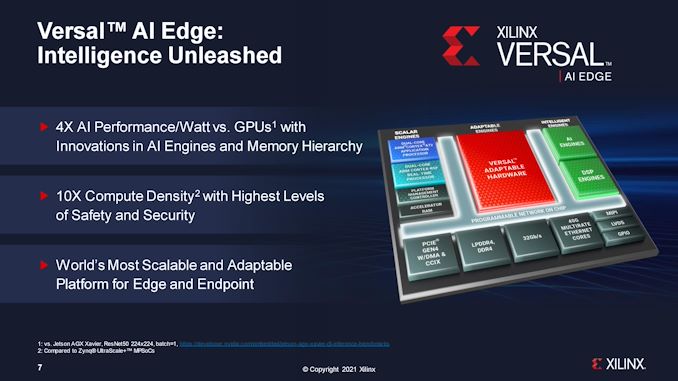

Xilinx’s conventional Versal system comprises quite a lot of scalar engines (Arm A72 cores for functions, Arm R5 core for real-time), clever engines (AI blocks, DSPs), adaptable engines (FPGA), and IO (PCIe, DDR, Ethernet, MIPI). For the largest Versal merchandise, these are massive and highly effective, facilitated by a programmable community on chip. For Versal’s AI Edge platform, there are two new options into the combination.

First is the usage of Accelerator SRAM positioned very near the scalar engines. Rather than conventional caches, it is a devoted configurable scratchpad with dense SRAM that the engines can entry at low latency slightly than traversing throughout the reminiscence bus. Traditional caches use predictive algorithms to drag knowledge from most important reminiscence, but when the programmer is aware of the workload, they will be sure that knowledge wanted on the most latency important factors can already be positioned near the processor earlier than the predictors know what to do. This four MB block has a deterministic latency,…