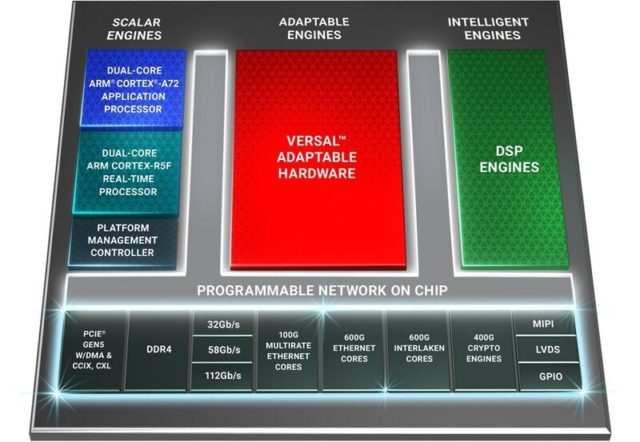

Versal is the business’s first adaptive compute acceleration platform (ACAP), a revolutionary new class of heterogeneous compute gadgets with capabilities that far exceed these of standard silicon architectures. Developed on TSMC’s 7-nanometer course of expertise, Versal Premium combines software program programmability with dynamically configurable {hardware} acceleration and pre-engineered connectivity and security measures to allow a quicker time-to-market. The Versal Premium sequence delivers as much as 3X increased throughput in comparison with present era FPGAs, with built-in Ethernet, Interlaken, and cryptographic engines that allow quick and safe networks. The sequence doubles the compute density of at the moment deployed mainstream FPGAs and offers the adaptability to maintain tempo with more and more various and evolving cloud and networking workloads.

“The Versal Premium series takes ACAPs to the next level delivering breakthrough networked hard IP integration enabling the development of single chip 400G and 800G solutions,” mentioned Kirk Saban, vice chairman of Product and Platform Marketing at Xilinx. “Targeting next-generation networks and cloud deployments, Versal Premium delivers superior bandwidth and compute density in a scalable platform that is readily programmable by hardware and software developers alike for optimized acceleration and reduced TCO.”

The Versal Premium sequence is constructed on a basis of the at the moment delivery Versal AI Core and Versal Prime ACAP sequence. New and distinctive to Versal Premium are 112 Gbps PAM4 transceivers, multi-hundred gigabit Ethernet and Interlaken connectivity, high-speed cryptography, and PCIe Gen5 with built-in DMA, supporting each CCIX and CXL. Together with the Vitis unified software program platform and Vivado Design Suite, the Versal Premium sequence gives a whole resolution stack for {hardware} and software program builders for optimum productiveness.

Faster, More Secure Networks

Greatly elevated community site visitors from 5G community rollout is driving demand for power-optimized throughput and compute density inside the current footprint and energy envelopes. The Versal Premium sequence addresses these challenges by delivering as much as 9Tb/s of scalable, adaptable serial bandwidth. This is achieved by using 112G PAM4 transceivers and built-in connectivity for core, metro and information heart interconnect (DCI) infrastructure that doubles bandwidth density per port and cut back latency by as much as 50 p.c.

The pre-engineered connectivity allows safe, multi-terabit Ethernet with the pliability to help a wide range of information charges and protocols. Channelized Ethernet cores ship as much as 5 Tb/s of throughput in a minimized footprint and high-speed cryptography engines present as much as 1.6 Tb/s of encrypted line-rate throughput and help for AES-GCM-256/128, MACsec, and IPsec.

“As the demand on the core network continues to grow, the need for adaptable infrastructure hardware greatly increases. The new Versal Premium ACAP builds on Xilinx’s portfolio of high-performance and flexible products for communications networks,” mentioned Jim McGregor, principal analyst, TIRIAS Research. “With the integration of networked, power-optimized cores, Versal Premium will allow telco operators to build fast and secure networks while offering adaptable acceleration for new data-intensive workloads that are transforming networks and data centers.”

Adaptable Cloud Acceleration

The Versal Premium sequence is engineered to assist hyperscalers attain the very best ranges of acceleration…