At Samsung’s Tech Day 2018 they debuted a collaboration with Xilinx to develop Smart SSDs that may mix storage with FPGA-based compute accelerator capabilities. Their proof of idea prototype combining a Samsung SSD and Xilinx FPGA on a PCIe add-in card has advanced right into a 4TB U.2 drive that has accomplished buyer qualification and reached normal availability.

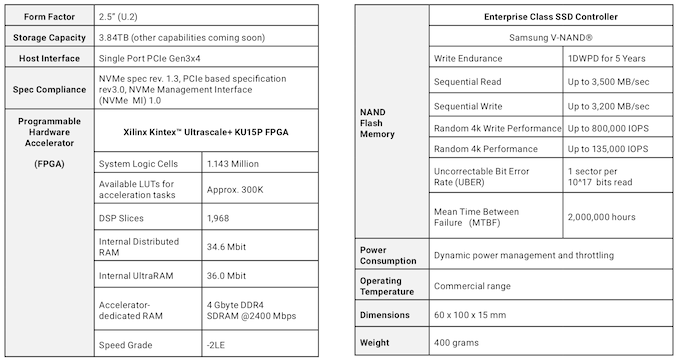

The Samsung SmartSSD CSD consists of all the heart of one among their high-end PCIe Gen3 enterprise SSDs, plus the most important FPGA from Xilinx’s Kintex Ultrascale+ (16nm) household and 4GB of DDR4 particularly for the FPGA to make use of. The SmartSSD CSD makes use of a portion of the FPGA as a PCIe change, so the FPGA and SSD every seem to the host system as separate PCIe endpoints and all PCIe visitors going to the SSD is first routed by way of the FPGA.

In a server geared up with dozens of enormous and quick SSDs, really making an attempt to utilize all that saved knowledge can result in bottlenecks with the CPU’s IO bandwidth or compute energy. Putting compute sources on every SSD means the compute capability and bandwidth scales with the variety of drives. Classic examples of compute duties to dump onto storage units are compression and encryption, however reconfigurable FPGA accelerators might help with a wider vary of duties.

Xilinx has been increase a library of IP for storage accelerators that prospects can use with the SmartSSD CSD, as a part of their Vitis libararies of constructing blocks and and Xilinx Storage Services turnkey options. Samsung has labored with Bigstream to implement Apache Spark analytics acceleration. Third celebration IP that has been developed for Xilinx’s Alveo accelerator playing cards can be ported to the SmartSSD CSD due to the frequent underlying FPGA platform, so IP like Eideticom’s NoLoad CSP are an choice.

The Samsung SmartSSD CSD is being manufactured by Samsung and bought by Xilinx, initially with 3.84TB capability however different sizes are deliberate.