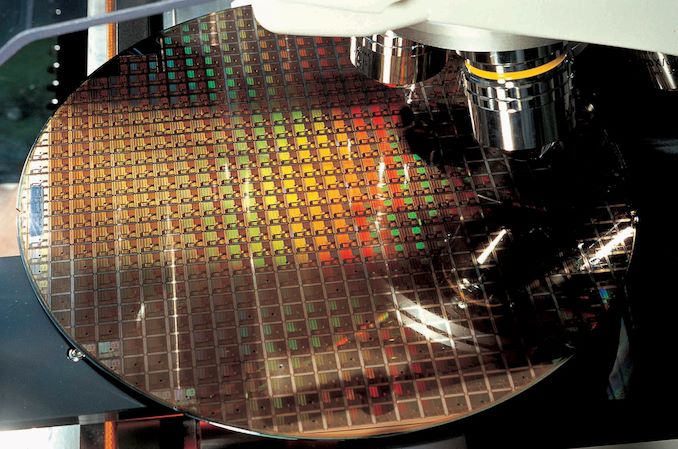

TSMC this week mentioned that it has accomplished improvement of instruments required for design of SoCs which can be made utilizing its 5 nm (CLN5FF, N5) fabrication know-how. The firm indicated that a few of its alpha clients (which use pre-production instruments and customized designs) had already began threat manufacturing of their chips utilizing its N5 manufacturing course of, which basically implies that the know-how is on-track for high-volume manufacturing (HVM) in 2020.

TSMC’s N5 is the corporate’s 2nd technology fabrication know-how that makes use of each deep ultraviolet (DUV) in addition to excessive ultraviolet (EUV) lithography. The course of can use EUVL on as much as 14 layers (a tangible progress from N7+, which makes use of EUVL on 4 non-critical layers) to allow vital enhancements when it comes to density. TSMC says that when in comparison with N7 (1st Gen 7 nm, DUV-only), N5 know-how will enable chip builders to shrink die space of their designs by ~45%, making transistor density ~1.8x greater. It may even enhance frequency by 15% (on the similar complexity and energy) or cut back energy consumption by 20% energy discount (on the similar frequency and complexity).

| Advertised PPA Improvements of New Process Technologies Data introduced by firms throughout convention calls, press briefings and in press releases |

||||||||

| TSMC | ||||||||

| 16FF+ vs 20SOC |

10FF vs 16FF+ |

7FF vs 16FF+ |

7FF vs 10FF |

7FF+ vs 7FF |

5FF vs 7FF |

|||

| Power | 60% | 40% | 60% | <40% | 10% | 20% | ||

| Performance | 40% | 20% | 30% | ? | similar (?) | 15% | ||

| Area Reduction | none | >50% | 70% | >37% | ~17% | 45% | ||

TSMC completed improvement of N5 a while in the past and its alpha clients with entry to pre-production instruments are already threat producing chips utilizing the know-how. Meanwhile, TSMC has finalized its 5 nm design rule handbook (DRM), course of design kits (PDKs), and SPICE (simulation program with built-in circuit emphasis) mannequin for these purchasers preferring to work with a secure model of design infrastructure.

Besides TSMC’s instruments, chip builders can even use a complete set of EDA (digital design automation) instruments from ANSYS, Cadence, Mentor Graphics, and Synopsys. TSMC says that EDA packages from the mentioned firms totally assist N5 DRM to make sure needed accuracy, routability for optimized energy, and different elements of the know-how. Obviously, all of the instruments have been licensed by the contract maker of semiconductors.

Finally, TSMC and its companions have additionally developeda complete N5 IP portfolio that’s at the moment centered totally on HPC and cell SoCs. TSMC’s Foundation IP consists of high-density and high-performance units of normal cell libraries and reminiscence compilers. Meanwhile, the corporate’s companions provide a wide range of IP cores for N5 SoCs, together with DDR, LPDDR, MIPI, PCIe, and USB PHYs.

“TSMC’s 5-nanometer technology offers our customers the industry’s most advanced logic process to address the exponentially growing demand for computing power driven by AI and 5G,” mentioned Cliff Hou, Vice President of Research & Development/Technology Development at TSMC. “5-nanometer technology requires deeper design-technology co-optimization. Therefore, we collaborate seamlessly with our ecosystem partners to ensure we deliver silicon-validated IP blocks and EDA tools ready for customer use. As always, we are committed to helping customers achieve first-time silicon success and faster time-to-market.”

All the instruments required for improvement of chips to be made utilizing N5 fabrication know-how can be found from TSMC and its companions proper now.

Related Reading

Source: TSMC