Of the a number of main modifications coming with HBM4 reminiscence, probably the most instant is the sheer width of the reminiscence interface. With the fourth-generation reminiscence customary transferring from an already huge 1024-bit interface to a ultra-wide 2048-bit interface, HBM4 reminiscence stacks will not be enterprise as ordinary; chip producers are going to wish to undertake extra superior packaging strategies than are used right this moment to accommodate the broader reminiscence.

As a part of its European Technology Symposium 2024 presentation, TSMC provided some contemporary particulars into the bottom dies it is going to be manufacturing for HBM4, which will likely be constructed utilizing logic processes. With TSMC planning to make use of variations of their N12 and N5 processes for this job, the corporate is anticipating to occupy a good place within the HBM4 manufacturing course of, as reminiscence fabs should not presently outfitted to economically produce such superior logic dies – if they will produce them in any respect.

For the primary wave of HBM4, TSMC is getting ready to make use of two fabrication processes: N12FFC+ and N5. While they serve the identical objective — integrating HBM4E reminiscence with next-generation AI and HPC processors — they’re going to be utilized in two alternative ways to attach reminiscence for high-performance processors for AI and HPC functions.

“We are working with key HBM memory partners (Micron, Samsung, SK Hynix) over advanced nodes for HBM4 full stack integration,” stated Senior Director of Design and Technology Platform at TSMC. “N12FFC+ cost effective base die can reach HBM for performance and N5 base die can provide even more logic with much lower power at HBM4 speeds.”

| TSMC Logic for HBM4 Base Die | ||||

| N12FFC+ | N5 | |||

| Area | 1X | 0.39X | ||

| Logic GHz @ energy | 1X | 1.55X | ||

| Power @ GHz | 1X | 0.35X | ||

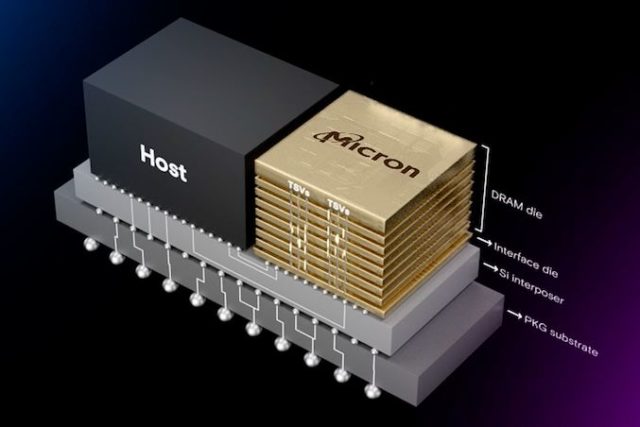

TSMC’s base die made on N12FFC+ fabrication course of (12nm FinFet Compact Plus, which formally belongs to a 12nm-class expertise, however it lays its roots from TSMC’s well-proven 16nm FinFET manufacturing node) will likely be used to put in HBM4 reminiscence stacks on a silicon interposer subsequent to system-on-chips (SoCs). TSMC believes that their 12FFC+ course of is well-suited to attain HBM4 efficiency, enabling reminiscence distributors to construct 12-Hi(48 GB) and 16-Hi stacks (64 GB), with per-stack bandwidth nicely as over 2 TB/second.

“We are also optimizing CoWoS-L and CoWoS-R for HBM4,” the Senior Director stated. “Both CoWoS-L and CoWoS-R [use] over eight layers to enable HBM4’s routing of over 2,000 interconnects with [proper] signal integrity.”

HBM4 base dies on N12FFC+ will likely be instrumental in constructing system-in-packages (SiPs) utilizing TSMC’s CoWoS-L or CoWoS-R superior packaging expertise, which supply interposers as much as 8x reticle dimension – sufficient house for as much as 12 HBM4 reminiscence stacks. At current, HBM4 can obtain information switch charges of 6 GT/s at currents of 14mA, in keeping with TSMC figures.

“We collaborate with EDA partners like Cadence, Synopsys, and Ansys to certify HBM4 channel signal integrity, IR/EM, and thermal accuracy,” the TSMC consultant defined.

Meanwhile, as an much more superior various, reminiscence producers will even have the choice of tapping TSMC’s N5 course of for his or her HBM4 base dies. N5-built base dies will pack much more logic, devour much less energy, and can provide even larger efficiency. But arguably a very powerful profit is that such a complicated course of expertise will allow are very small interconnect pitches, on the order of 6 to 9 microns. This will enable N5 base dies for use at the side of direct bonding, enabling HBM4 to be 3D stacked proper on prime of logic chips. Direct bonding stands to permit for even better reminiscence efficiency, which is anticipated to be a giant increase for AI and HPC chips which can be at all times scrounging for extra reminiscence bandwidth.

We already know that TSMC and SK…