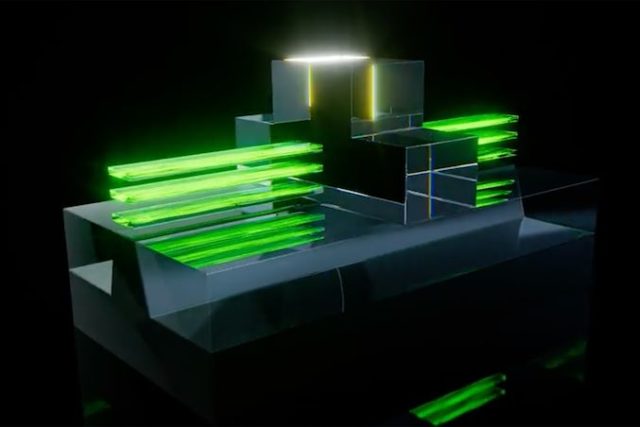

In addition to revealing its roadmap and plans regarding its present modern course of applied sciences, TSMC additionally shared progress of its N2 node as a part of its Symposiums 2024. The firm’s first 2nm-class fabrication node, and predominantly that includes gate-all-around transistors, in response to TSMC N2 has virtually achieved its goal efficiency and yield objectives, which locations it on monitor to enter high-volume manufacturing within the second half of 2025.

TSMC states that ‘N2 improvement is effectively on monitor and N2P is subsequent.’ In specific, gate-all-around nanosheet gadgets presently obtain over 90% of their anticipated efficiency, whereas yields of 256 Mb SRAM (32 MB) gadgets already exceeds 80%, relying on the batch. All of this for a node that’s over a 12 months away from mass manufacturing.

Meanwhile, common yield of a 256 Mb SRAM was round 70% as of March, 2024, up from round 35% in April, 2023. Device efficiency has additionally been bettering with increased frequencies being achieved whereas retaining energy consumption in examine.

Chip designer curiosity in direction of TSMC’s first 2nm-class gate-all-around nanosheet transistor-based know-how is critical, too. The variety of new tape-outs (NTOs) within the first 12 months of N2 is over two-times increased than it was for N5. Though with that stated, given TSMC’s shut working relationship with a handful of high-volume distributors – most notably Appe – NTOs generally is a very deceptive determine because the first 12 months of a brand new node at TSMC is capability constrained, and consequently the majority of that capability goes to TSMC’s precedence companions.

Meanwhile, there have been significantly extra N5 tapeouts in its second 12 months (some the place N5P, in fact) and N2 guarantees to have 2.6X extra NTOs in its second 12 months. So the node certainly seems to be fairly promising. In truth, primarily based on TSMC’s slides (which we’re sadly not in a position to republish), N2 is extra standard than N3 when it comes to NTOs each within the first and the second years of existence.

When it involves the second 12 months of N2, within the second half of 2026 TSMC plans to roll out its N2P know-how, which guarantees further efficiency and energy advantages. N2P is predicted to enhance frequency by 15% – 20%, cut back energy consumption by 30% – 40%, and enhance chip density by over 1.15 instances in comparison with N3E, important advantages to maneuver to all-new GAA nanosheet transistors.

Finally, for these corporations that want the perfect in efficiency, energy, and density, TSMC is poised to supply their A16 course of in 2026. That node may even herald bottom energy supply, which can add prices, however is predicted to drastically enhance efficiency effectivity and scaling.

![[Interview] ‘Bixby Will Be Your Go-To Starting Point for](https://loginby.com/itnews/wp-content/uploads/2026/04/1775675971_Interview-‘Bixby-Will-Be-Your-Go-To-Starting-Point-for-100x75.jpg)