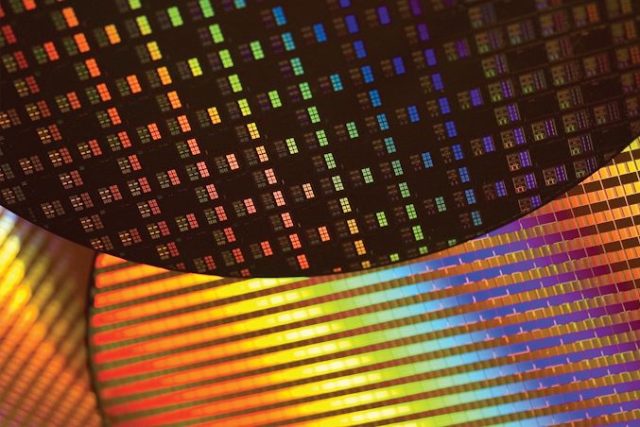

Although TSMC cannot declare to be the primary fab to make use of excessive UV (EUV) lithography – that title goes to Samsung – they do get to say to be the most important. As a outcome, the corporate has developed important expertise with EUV through the years, permitting TSMC to refine how they use EUV tooling to each enhance productiveness/uptime, and to chop down on the prices of utilizing the ultra-fine instruments. As a part of the corporate’s European Technology Symposium this week, they went right into a bit extra element on their EUV utilization historical past, and their progress on additional integrating EUV into future course of nodes.

When TSMC began making chips utilizing EUV lithography in 2019 on its N7+ course of (for Huawei’s HiSilicon), it held 42% of the world’s put in base of EUV instruments, and whilst ASML ramped up shipments of EUV scanners in 2020, TSMC’s share of EUV installations truly elevated to 50%. And leaping forward to 2024, the place the variety of EUV litho methods at TSMC has elevated by 10-fold from 2019, TSMC is now 56% of the worldwide EUV put in base, regardless of Samsung and Intel ramping up their very own EUV manufacturing. Suffice it to say, TSMC decided to go in laborious on EUV early on, and because of this they nonetheless have the lion’s share of EUV scanners as we speak.

Notably, TSMC’s EUV wafer manufacturing has elevated by a fair bigger issue; TSMC now pumps out 30 occasions as many EUV wafers as they did in 2019. Compared to the mere 10x improve in instruments, TSMC’s 30x leap in manufacturing underscores how TSMC has been capable of improve their EUV productiveness, scale back service occasions, and fewer software downtimes general. Apparently, this has all been achieved utilizing the corporate’s in-house developed improvements.

| TSMC’s Leadership in EUV High Volume Manufacturing Data by TSMC (Compiled by AnandTech) |

||||

| 2019 | 2023 | |||

| Cumulative Tools | 1X | 10X | ||

| Share of Global EUV Installed Base | 42% | 56% | ||

| EUV Wafer Output | 1X | 30X | ||

| Wafer per Day per EUV Tool | 1X | 2X | ||

| Reticle Particle Contamination | 1X | 0.1X | ||

TSMC says that it has managed to extend wafer-per-day-per-tool productiveness of its EUV methods by two occasions since 2019. To achieve this, the corporate optimized the EUV publicity dose and the photoresist it makes use of. In addition, TSMC drastically refined its pellicles for EUV reticles, which elevated their lifespan by 4 occasions (i.e., will increase uptime), elevated output per pellicle by 4.5 occasions, and lowered defectivity by large 80 occasions (i.e., improves productiveness and will increase uptime). For apparent causes, TSMC doesn’t disclose the way it managed to enhance its pellicle know-how so considerably, however maybe over time the corporate’s engineers are going to share this with academia.

| TSMC’s EUV Pellicle Technology vs. Commercial Data by TSMC (Compiled by AnandTech) |

||||

| Commercial | TSMC (Claimed) | |||

| Output | 1X | 4.5X | ||

| Defectivity | 1X | 0.0125X | ||

| Lifespan | 1X | 4X | ||

EUV lithography methods are additionally infamous for his or her energy consumption. So, along with bettering productiveness of EUV instruments, the corporate additionally managed to cut back the ability consumption of its EUV scanners by 24% by undisclosed ‘progressive vitality saving methods.’ And the corporate is not completed there: they’re planning to enhance vitality effectivity per wafer per EUV software by 1.5 occasions by 2030.

Considering all of the refinements that TSMC has managed to attain with Low-NA EUV lithography by now, it isn’t terribly stunning that the corporate is kind of assured that it will possibly proceed to supply cutting-edge chips sooner or later. Whereas rival Intel has gone all-in on High-NA EUV for his or her future, sub-18A nodes, TSMC is seeking to leverage their highly-optimized and time-tested Low-NA EUV tooling as an alternative, avoiding the potential pitfalls of a serious…

![[Interview] ‘Bixby Will Be Your Go-To Starting Point for](https://loginby.com/itnews/wp-content/uploads/2026/04/1775675971_Interview-‘Bixby-Will-Be-Your-Go-To-Starting-Point-for-100x75.jpg)