At TSMC’s annual Technology Symposium, the Taiwanese semiconductor producer detailed traits of its future 3nm course of node in addition to laying out a roadmap for 5nm successors within the type of N5P and N4 course of nodes.

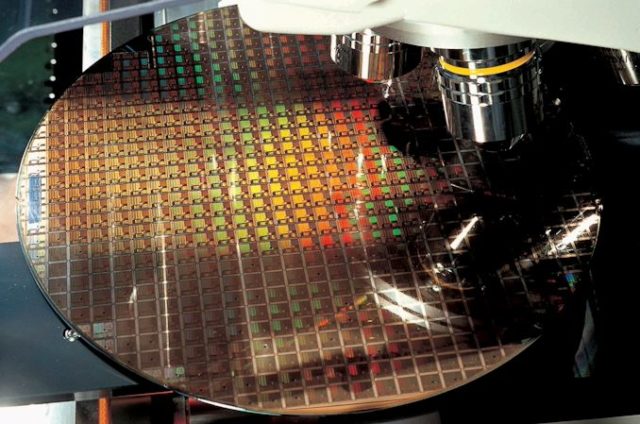

Starting off with TSMC’s upcoming N5 course of node which represents its 2nd technology deep-ultraviolet (DUV) and extreme-ultraviolet (EUV) course of node after the hardly ever used N7+ node (Used by the Kirin 990 SoC for instance). TSMC has been in mass manufacturing for a number of months now as we’re anticipating silicon transport to clients at this second with shopper merchandise transport this 12 months – Apple’s next-generation SoCs being the probably first candidates for the node.

TSMC particulars that N5 presently is progressing with defect densities one quarter forward of N7, with the brand new node having higher yields on the time of mass manufacturing than each their predecessor main nodes N7 and N10, with a projected defect density that’s presupposed to proceed to enhance previous the historic traits of the final two generations.

The foundry is making ready a brand new N5P node that’s based mostly on the present N5 course of that extends its efficiency and energy effectivity with a 5% pace acquire and a 10% energy discount.

Beyond N5P, TSMC can also be introducing the N4 node that represents an additional evolution from the N5 course of, using additional EUV layers to cut back masks, with minimal migration work required by chip designers. We’ll be seeing N4 danger manufacturing begin in 4Q21 for quantity manufacturing later in 2022.

Today’s largest information was TSMC’s disclosure on their subsequent huge leap previous the N5 course of node technology household, which is the 3nm N3 node. We’ve heard that TSMC had been engaged on defining the node again final 12 months with progress going effectively.

Contrary to Samsung’s 3nm course of node which makes use of GAA (Gate-all-around) transistor buildings, TSMC will as an alternative be sticking with FinFET transistors and counting on “innovative features” to allow them to attain the full-node scaling that N3 guarantees to carry.

| Advertised PPA Improvements of New Process Technologies Data introduced throughout convention calls, occasions, press briefings and press releases |

||||||||

| TSMC | ||||||||

| N7 vs 16FF+ |

N7 vs N10 |

N7P vs N7 |

N7+ vs N7 |

N5 vs N7 |

N5P vs N5 |

N3 vs N5 |

||

| Power | -60% | <-40% | -10% | -15% | -30% | -10% | -25-30% | |

| Performance | +30% | ? | +7% | +10% | +15% | +5% | +10-15% | |

| Logic Area

Reduction % (Density) |

70% |

>37% |

– |

~17% |

0.55x

-45% (1.8x) |

– |

0.58x

-42% (1.7x) |

|

| Volume Manufacturing |

|

|

|

Q2 2019 |

Q2 2020 | 2021 | H2 2022 | |

Compared to it’s N5 node, N3 guarantees to enhance efficiency by 10-15% on the identical energy ranges, or cut back energy by 25-30% on the identical transistor speeds. Furthermore, TSMC guarantees a logic space density enchancment of 1.7x, which means that we’ll see a 0.58x scaling issue between N5 and N3 logic. This aggressive shrink doesn’t straight translate to all buildings, as SRAM density is disclosed at solely getting a 20% enchancment which might imply a 0.8x scaling issue, and analog buildings scaling even worse at 1.1x the density.

Modern chip designs are very SRAM-heavy with a rule-of-thumb ratio of 70/30 SRAM to logic ratio, so on a chip degree the anticipated die shrink would solely be ~26% or much less.

N3 is deliberate to enter danger manufacturing in 2021 and enter quantity manufacturing in 2H22. TSMC’s disclosed course of traits on N3 would monitor carefully with Samsung’s disclosures on 3GAE when it comes to energy and efficiency, however would lead extra significantly when it comes to density.

We’ll be posting extra detailed content material from TSMC’s Technology…