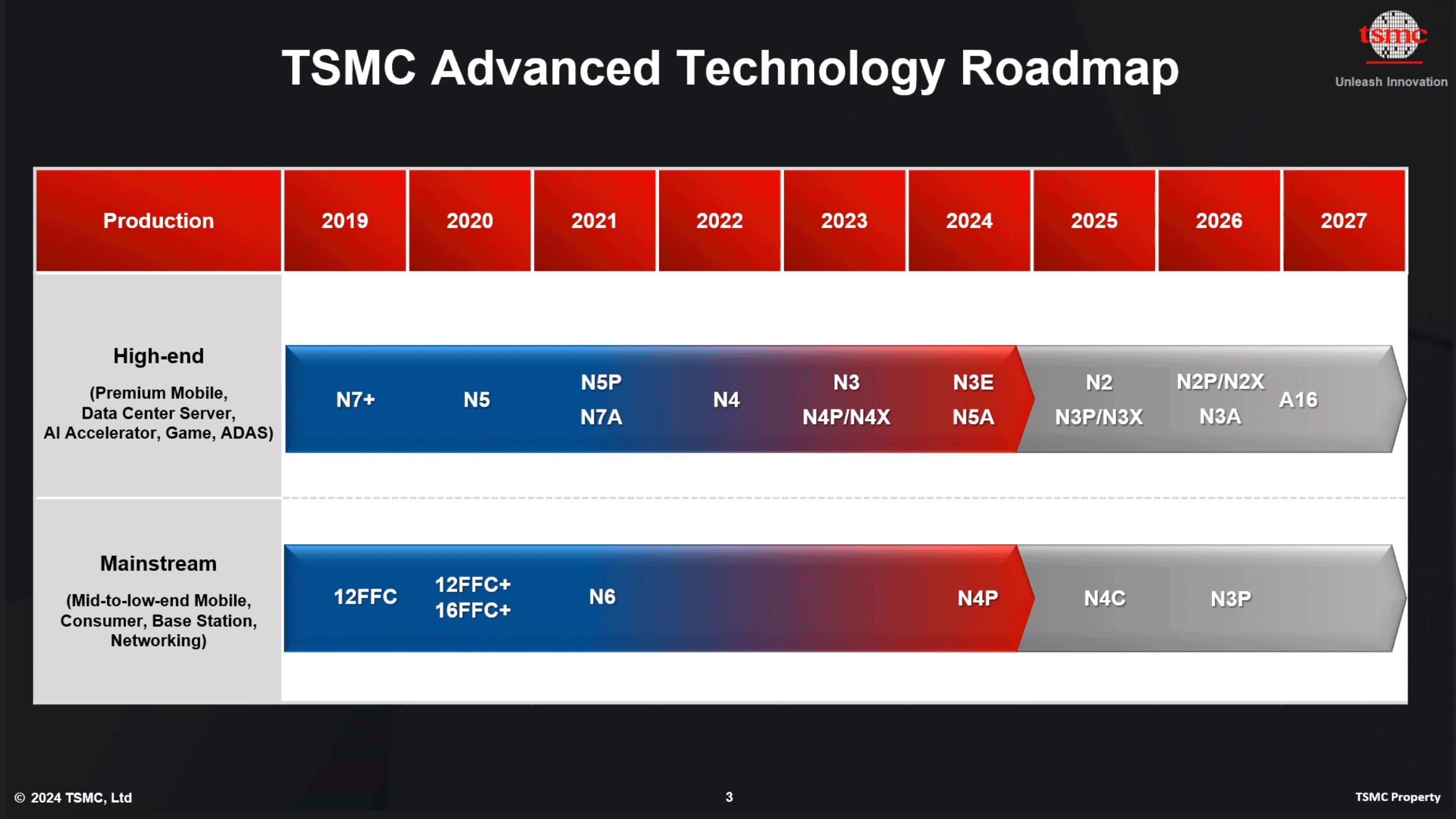

Taiwan Semiconductor Manufacturing Co. offered a number of necessary updates about its upcoming course of applied sciences at its North American Technology Symposium 2024. At a excessive stage, TSMC’s 2 nm plans stay largely unchanged: the corporate is on monitor to begin quantity manufacturing of chips on it is first-generation GAAFET N2 node within the second half of 2025, and N2P will succeed N2 in late 2026 – albeit with out the previously-announced bottom energy supply capabilities. Meanwhile, the entire N2 household will probably be including TSMC’s new NanoFlex functionality, which permits chip designers to combine and match cells from completely different libraries to optimize efficiency, energy, and space (PPA).

One of the important thing bulletins of the occasion is TSMC’s NanoFlex expertise, which will probably be part of the corporate’s full N2 household of manufacturing nodes (2 nm-class, N2, N2P, N2X). NanoFlex will allow chip designers to combine and match cells from completely different libraries (excessive efficiency, low energy, space environment friendly) throughout the similar block design, permitting designers to tremendous tune their chip designs to enhance efficiency or decrease energy consumption.

TSMC’s up to date N3 fabrication course of already helps an analogous functionality known as FinFlex, which additionally permits designers to make use of cells from completely different libraries. But since N2 depends on gate-all-around (GAAFET) nanosheet transistors, NanoFlex offers TSMC some further controls: firstly, TSMC can optimize channel width for efficiency and energy after which construct brief cells (for space and energy effectivity) or tall cells (for as much as 15% increased efficiency).

When it involves timing, TSMC’s N2 is ready to enter threat manufacturing in 2025 and high-volume manufacturing (HVM) within the second half of 2025, so it seems to be like we’re going to see N2 chips in retail units in 2026. Compared to N3E, TSMC expects N2 to extend efficiency by 10% to 15% on the similar energy, or scale back energy consumption by 25% to 30% on the similar frequency and complexity. As for chip density, the foundry is taking a look at a 15% density enhance, which is an efficient diploma of scaling by up to date requirements.

N2 will probably be adopted by performance-enhanced N2P, in addition to the voltage-enhanced N2X in 2026. Although TSMC as soon as stated that N2P would add bottom energy supply community (BSPDN) in 2026, it seems to be like this is not going to be the case and N2P will use common energy supply circuitry. The purpose for that is unclear, however it seems to be like the corporate determined to not add a expensive characteristic to N2P, however to order it to its next-generation node, which will even be accessible to clients in late 2026.

N2 remains to be anticipated to characteristic a serious innovation associated to energy: super-high-performance metal-insulator-metal (SHPMIM) capacitors, that are are being added to enhance energy provide stability. The SHPMIM capacitor provides greater than twice the capability density of TSMC’s current super-high-density metal-insulator-metal (SHDMIM) capacitor. Additionally, the brand new SHPMIM capacitor cuts sheet resistance (Rs in Ohm/sq.) and through resistance (Rc) by 50% in comparison with its predecessor.