This week as a part of the annual Hot Chips semiconductor convention, Samsung’s reminiscence division has introduced a poster/slides on a challenge it’s at present engaged on with spectacular end-point outcomes. The firm particulars a 512 GB module of DDR5 reminiscence, working at DDR5-7200, designed for server and enterprise use. This is a step up from the 256 GB modules on the prime finish of the market at present, however to get there, Samsung has been introducing some new options and performance.

As per customary DDR5 specs, the modules will run at 1.1 volts with customary JEDEC DDR5-7200 timings, nonetheless even JEDEC has not declared an official DDR5-7200 customary at this stage, selecting solely to go to DDR5-6400. There are placeholders for future requirements, resembling DDR5-7200, and primarily based on how the latencies improve from slower pace to larger pace, these needs to be within the realm of 50-50-50 to 60-60-60*.

*There are three variants for every DDR5 customary – A, B, or C.

DDR5-6400A is 46-46-46 for instance, however

DDR5-6400C is 56-56-56.

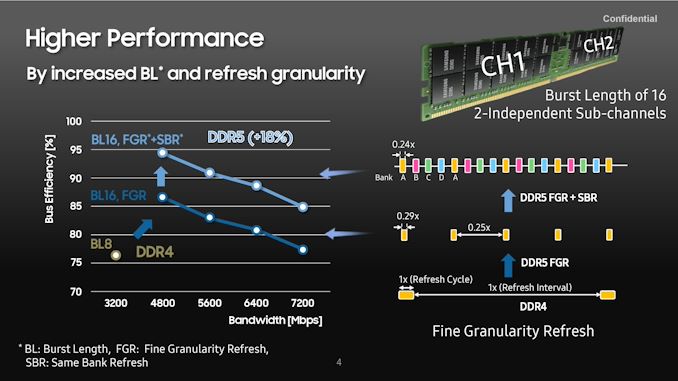

As a part of the presentation, Samsung states that the introduction of Same-Bank refresh (SBR) into its DDR5 will improve the effectivity of the DRAM bus connectivity by nearly 10%, with DDR4-4800 exhibiting the most effective effectivity when it comes to vitality from bit.

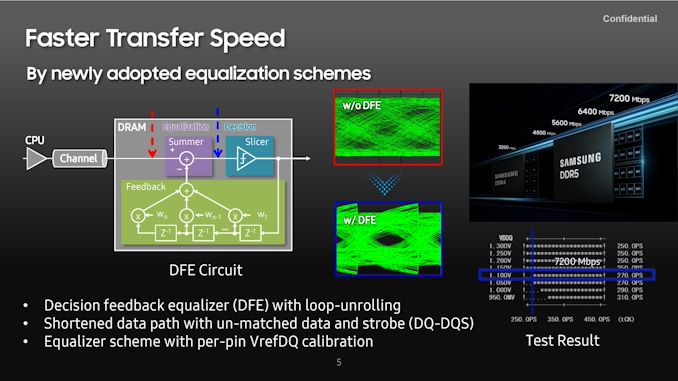

In order to help the upper reminiscence switch charges of DDR5, Samsung has launched a brand new DFE (Decision Feedback Equalizer) for higher sign stability. It permits for a extra variable data-path location, in addition to per-pin calibration methods.

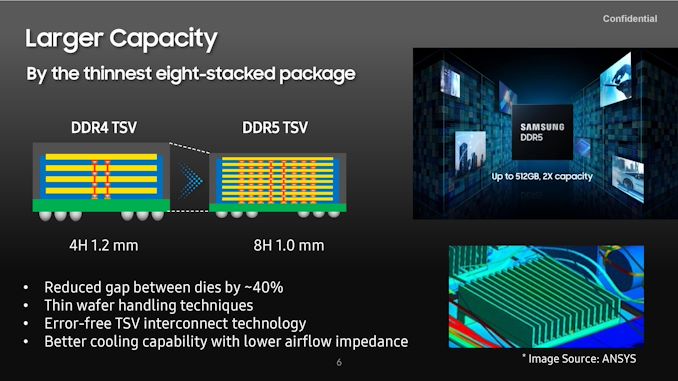

One of the large issues about rising capability in reminiscence is that you find yourself stacking extra reminiscence collectively. For their half, Samsung is stating that they’ll stack eight DDR5 dies collectively and nonetheless be smaller than four dies of DDR4. This is achieved by thinning every die, but additionally new through-silicon-via connection topographies that enable for a diminished hole between dies of as much as 40%. This is partnered by new cooling applied sciences between dies to help with thermal efficiency.

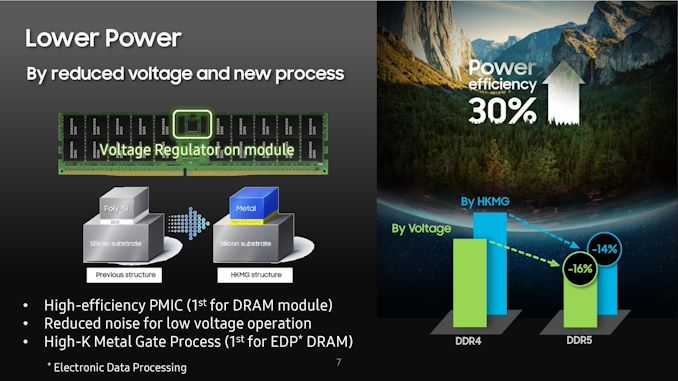

On energy, we’ve recognized that one of many drivers for JEDEC’s latest reminiscence specs is decrease energy, and for DDR5 the key factor other than the decrease voltage is to deliver the voltage regulator from the motherboard on to the reminiscence module. This permits for the reminiscence module producer to extra tightly management the ability necessities and consumption of the reminiscence, particularly ought to the motherboard be a really low-cost mannequin which may skimp on valued parts on the voltage regulation stage. For this 512 GB module, Samsung is utilizing a high-efficiency Power Management IC (PMIC) – Samsung as an organization has quite a lot of PMIC expertise by means of its different digital divisions, so little doubt they’ll get excessive effectivity right here. Samsung additionally states that its PMIC has diminished noise, permitting for decrease voltage operation, and in addition makes use of a High-Ok Metal Gate course of (launched on CPUs at 45nm) in a primary for DRAM.

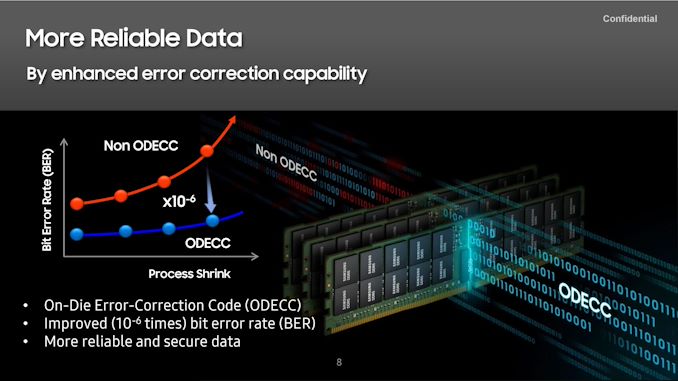

One of the speaking factors on DDR5 has been the on-die ECC (ODECC) performance, in-built to DDR5 to assist enhance yields of reminiscence by initiating a per-die ECC topology. The confusion lies in that this isn’t a real ECC enablement on a DDR5 module, which nonetheless requires further bodily reminiscence and a protected bus. But on the subject of ODECC, Samsung is showcasing an enchancment on its bit-error fee of 10-6, or an element of one million decrease BER. How a lot of that is required by the DDR5 JEDEC specification is unclear at this level, however it’s nonetheless an excellent route to have.

At the top of the slide deck from Samsung, it states that its first 512 GB module needs to be prepared for mass manufacturing by the top of 2021 – it’s unclear if this can be a DDR5-7200 module or one thing else, because the slide may very well be interpreted in a different way. But one of many key facets to…

![[Editorial] How APV Is Elevating Mobile Video to](https://loginby.com/itnews/wp-content/uploads/2026/04/1776281191_Editorial-How-APV-Is-Elevating-Mobile-Video-to-100x75.jpg)