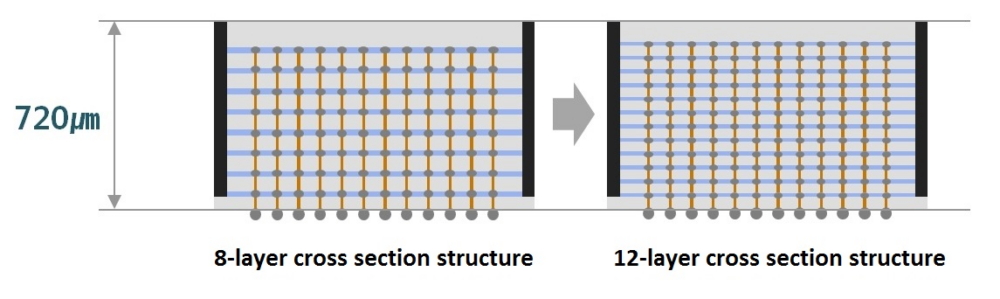

The new know-how permits for the stacking of 12 DRAM chips utilizing greater than

60,000 TSV holes, whereas sustaining the identical thickness as present 8-layer chips

Samsung Electronics, a world chief in superior semiconductor know-how, at the moment introduced that it has developed the business’s first 12-layer 3D-TSV (Through Silicon Via) know-how.

Samsung’s new innovation is taken into account one of the vital difficult packaging applied sciences for mass manufacturing of high-performance chips, because it requires pinpoint accuracy to vertically interconnect 12 DRAM chips by means of a three-dimensional configuration of greater than 60,000 TSV holes, every of which is one-twentieth the thickness of a single strand of human hair.

The thickness of the package deal (720㎛) stays the identical as present 8-layer High Bandwidth Memory-2 (HBM2) merchandise, which is a considerable development in element design. This will assist clients launch next-generation, high-capacity merchandise with increased efficiency capability with out having to alter their system configuration designs.

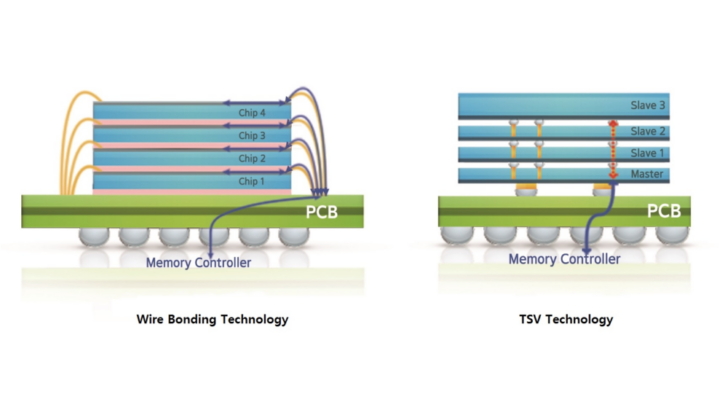

In addition, the 3D packaging know-how additionally encompasses a shorter knowledge transmission time between chips than the at the moment current wire bonding know-how, leading to considerably sooner velocity and decrease energy consumption.

“Packaging technology that secures all of the intricacies of ultra-performance memory is becoming tremendously important, with the wide variety of new-age applications, such as artificial intelligence (AI) and High Power Computing (HPC),” mentioned Hong-Joo Baek, government vice chairman of TSP (Test & System Package) at Samsung Electronics.

“As Moore’s law scaling reaches its limit, the role of 3D-TSV technology is expected to become even more critical. We want to be at the forefront of this state-of-the-art chip packaging technology.”

Relying on its 12-layer 3D-TSV know-how, Samsung will supply the best DRAM efficiency for purposes which can be data-intensive and very high-speed.

Also, by growing the variety of stacked layers from eight to 12, Samsung will quickly have the ability to mass produce 24-gigabyte (GB)* High Bandwidth Memory, which supplies 3 times the capability of 8GB excessive bandwidth reminiscence in the marketplace at the moment.

Samsung will have the ability to meet the quickly rising market demand for high-capacity HBM options with its cutting-edge 12-layer 3D TSV know-how and it hopes to solidify its management within the premium semiconductor market.

*8GB mass-production product= 8Gb x Eight layers, 24GB developed product= 16Gb x 12 layers

*PKG cross part construction

*Wire bonding vs TSV know-how