All of the world’s main superpowers have a vested curiosity in constructing their very own customized silicon processors. The very important ingredient to this permits the superpower to wean itself off of US-based processors, assure there aren’t any supplemental backdoors, and if wanted add their very own. As we now have seen with China, customized chip designs, x86-based joint ventures, or Arm derivatives appear to be the order of the day. So in comes Russia, with its customized Elbrus VLIW design that appears to have its roots in SPARC.

Russia has been creating processors known as Elbrus for various years now. For these of us outdoors Russia, it has principally been a giant query mark as to what’s really beneath the hood – these chips are constructed for customized servers and workplace PCs, typically on the route of the Russian authorities and its necessities. We have had glimpses of the design, because of paperwork from Russian supercomputing occasions, nonetheless these are just a few years previous now. If you aren’t in Russia, you’re unlikely to ever get your palms on one at any fee. However, it not too long ago got here to our consideration of a brand new programming information listed on-line for the newest Elbrus-8CB processor designs.

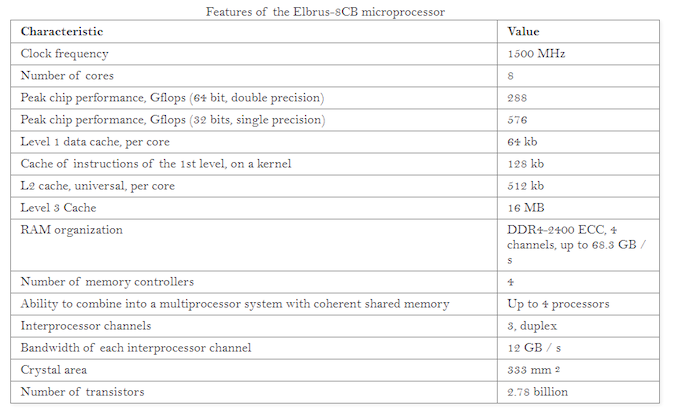

The newest Elbrus-8CB chip, as detailed within the new on-line programming information printed this week, constructed on TSMC’s 28nm, is a 333 mm2 design that includes Eight cores at 1.5 GHz. Peak throughput based on the paperwork states 576 GFLOPs of single precision, with the chip providing 4 channels of DDR4-2400, good for 68.three GB/s. The L1 and L2 caches are personal, with a 64 kB L1-D cache, a 128 kB L1-I cache, and a 512 kB L2 cache. The L3 cache is shared between the cores, at 2 MB/core for a complete of 16 MB. The processor additionally helps 4-way server multiprocessor combos, though it doesn’t say on what protocol or what bandwidth.

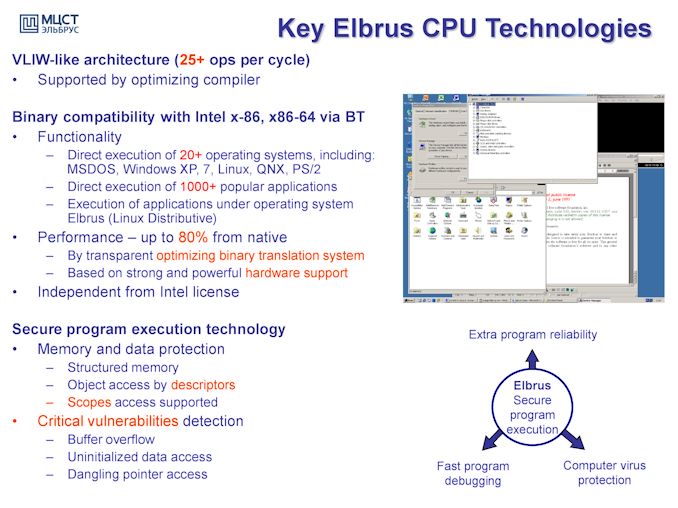

It is a compiler centered design, very similar to another advanced chips, in that many of the optimizations occur on the compiler stage. Based on compiler first designs up to now, that sometimes doesn’t make for a profitable product. Documents from 2015 state {that a} persevering with aim of the Elbrus design is x86 and x86-64 binary translation with solely a 20% overhead, permitting full help for x86 code in addition to x86 working programs, together with Windows 7 (this may increasingly have been up to date since 2015).

The core has six execution ports, with many ports being multi-capable. For instance, 4 of the ports could be load ports, and two of the ports could be retailer ports, however all of them can do integer operations and most can do floating level operations. Four of the ports can do comparability operations, and people 4 ports may also do vector compute.

This quick information submit is just not meant to be a whole breakdown of the Elbrus capabilities – we now have amusingly joked internally at what frequency a Cortex X1 with x86 translation would match the capabilities of the 8-core Elbrus, nonetheless customers who need to familiarize yourself with the design can open and browse the documentation on the following handle:

http://ftp.altlinux.org/pub/people/mike/elbrus/docs/elbrus_prog/html/index.html

The greater query goes to be how possible any of those state-funded processor growth tasks are going to succeed at scale. State-funded teams ought to, theoretically, be the most effective funded, nonetheless even with all the cash on the earth, engineers are nonetheless required to get issues completed. Even if there finally ends up being a brand new super-CPU for a given superpower, there’ll all the time be vested pursuits in an quantity of safety although obscurity, particularly if the {hardware} is designed particularly to cater to state-secret ranges of compute. There’s additionally the added complication of the US authorities tightening its screws round TSMC and ASML to not settle for orders from particular corporations -…