The newest enhancements to the HBM2 customary will clearly be appreciated by builders of reminiscence bandwidth-hungry ASICs, nonetheless as a way to add assist of HBM2E to their designs, they’re additionally going to want an applicable controller in addition to bodily interface. For many firms creating of such IP in-house doesn’t make monetary sense, so Rambus has designed a highly-integrated HBM2E answer for licensing.

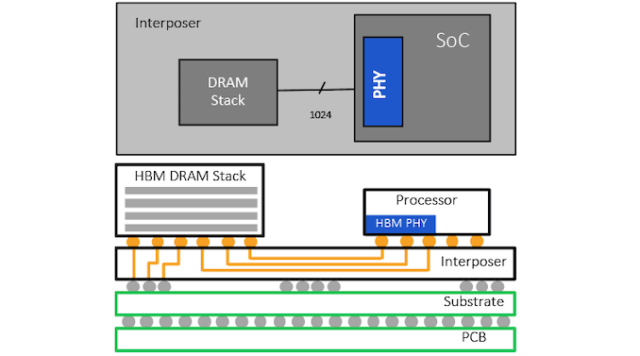

The HBM2E customary helps 12-Hi DRAM stacks in addition to reminiscence gadgets of as much as 16 Gbps, thus enabling to construct as much as 24 GB stacks utilizing a 1024-bit bus. At the identical time, the brand new specification formally helps information charges of as much as 3.2 Gbps, which leads to 409.6 GB/s bandwidth per stack. Rambus’s HBM2E answer features a controller that may work with 12-Hi KGSDs (identified good stack dies) in addition to a verified 1024-bit PHY that helps speeds of as much as 3.2 Gbps.

The Rambus HBM2E controller core (initially developed by Northwest Logic) is DFI 3.1 appropriate (with applicable extensions) and helps AXI, OCP or proprietary interfaces to hook up with integrator logic. Meanwhile, the controller additionally helps Look-Ahead command processing (a normal approach to trim latencies) in addition to channel densities of as much as 24 Gb.

Licensees of Rambus’s HBM2E answer will get every little thing they should combine it into their designs, together with supply code of the controller (in a bid to synthesize it for a specific course of know-how) in addition to fully-characterized laborious macros (GDSII) of the interface. Alternatively, engineers from Rambus will help combine the HBM2E IP assist for a charge.

Source: Rambus