“With this achievement by Rambus, designers of AI and HPC systems can now implement systems using the world’s fastest HBM2E DRAM running at 3.6 Gbps from SK hynix,” stated Uksong Kang, vp of product planning at SK hynix. “In July, we announced full-scale mass-production of HBM2E for state-of-the-art computing applications demanding the highest bandwidth available.”

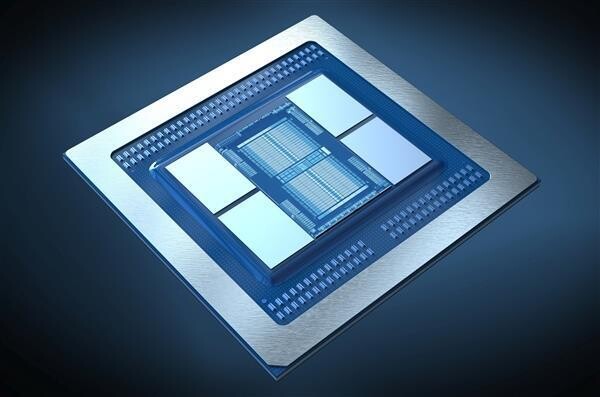

The fully-integrated, production-ready Rambus HBM2E reminiscence subsystem runs at 4 Gbps with out PHY voltage overdrive. Rambus teamed with SK hynix and Alchip to implement the HBM2E 2.5D system to validate in silicon the Rambus HBM2E PHY and Memory Controller IP utilizing TSMC’s N7 course of and CoWoS (Chip-on-Wafer-on-Substrate) superior packaging applied sciences. Co-designing with the engineering group from Rambus, Alchip led the interposer and package deal substrate design.

“This advancement of Rambus and its partners, using TSMC’s advanced process and packaging technologies, is another important achievement of our ongoing collaboration with Rambus,” stated Suk Lee, senior director of the Design Infrastructure Management Division at TSMC. “We look forward to a continued partnership with Rambus to enable the highest performance in AI/ML and HPC applications.”

“Alchip brought a demonstrated track record of success in 7nm and 2.5D package design to this initiative,” stated Johnny Shen, CEO of Alchip Technologies. “We’re extremely proud of our contributions to Rambus’ breakthrough achievement.”

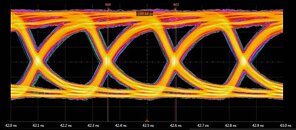

Rambus has 30 years of high-speed reminiscence design utilized to probably the most demanding computing purposes. Its famend sign integrity experience was key to reaching an HBM2E reminiscence interface able to 4 Gbps operation. This raises a brand new benchmark for assembly the insatiable bandwidth necessities of AI/ML coaching.

“With silicon operation up to 4 Gbps, designers can future-proof their HBM2E implementations and can be confident of ample margin for 3.6 Gbps designs,” stated Matthew Jones, senior director and common supervisor of IP cores at Rambus. “As part of every customer engagement, Rambus provides reference designs for the 2.5D package and interposer to ensure first-time right implementations for mission-critical AI/ML designs.”

Benefits of the Rambus HBM2E Memory Interface (PHY and Controller):

- Achieves the business’s highest pace of 4 Gbps per pin, delivering a system bandwidth of 460 GB from a single 3.6 Gbps HBM2E DRAM 3D gadget.

- Fully-integrated and verified HBM2E PHY and Controller reduces ASIC design complexity and speeds time to market

- Includes 2.5D package deal and interposer reference design as a part of IP license

- Provides entry to Rambus system and SI/PI specialists serving to ASIC designers to make sure most sign and energy integrity for units and techniques

- Features LabStation growth atmosphere that permits fast system bring-up, characterization and debug

- Supports high-performance purposes together with state-of-the-art AI/ML coaching and high-performance computing (HPC) techniques

For extra info on the Rambus Interface IP, together with our PHYs and Controllers, please go to rambus.com/interface-ip.