It’s been a bit over a 12 months since we coated Marvell’s OCTEON TX2 infrastructure processors, and since then, the ecosystem has been evolving in a particularly quick method – each inside Marvell and out of doors. Today, we’re masking the brand new technology OCTEON 10 household of DPUs, an entire new household of SoCs, constructed upon TSMC’s 5nm course of node and likewise for the that includes for the primary time Arm’s new Neoverse N2 processors.

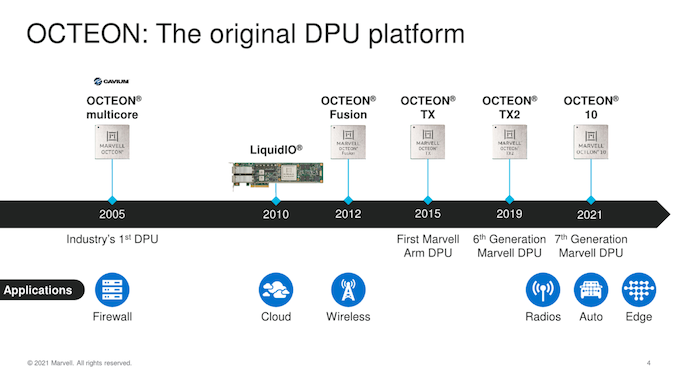

Starting off with a little bit of historical past and nomenclature, Marvell is adopting the “DPU” time period for this class of chip and accelerator kind. The earlier technology OCTEON TX and OCTEON TX2 already had been DPUs in every little thing however identify, beforehand merely being referenced as “infrastructure processors”. With the current trade rising reputation of the time period in addition to competitor options being propped up, it appears we’re seeing the DPU time period now being extensively accepted nomenclature for such a versatile chip design, outlined by the truth that it’s an entity that helps course of and transfer information whereas it travels by the community.

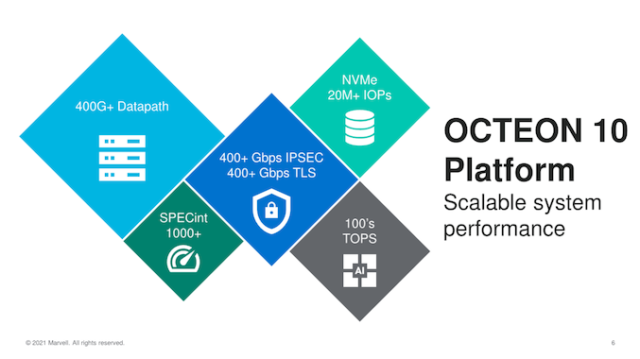

Starting with an summary, the brand new OCTEON 10 usually options the identical versatile array of constructing blocks we’ve seen within the earlier technology, this time upgraded to the brand new state-of-the-art IP blocks, and likewise introducing some new options similar to built-in machine studying inference engine, new inline and crypto processors in addition to vector packet processors, all capable of operated in a virtualised method.

This can be Marvell’s first TSMC N5P silicon design, truly the primary DPU of its sort on the brand new course of, and likewise the primary publicly introduced Neoverse N2 implementation, that includes the latest PCIe 5.zero I/O capabilities in addition to DDR5 assist.

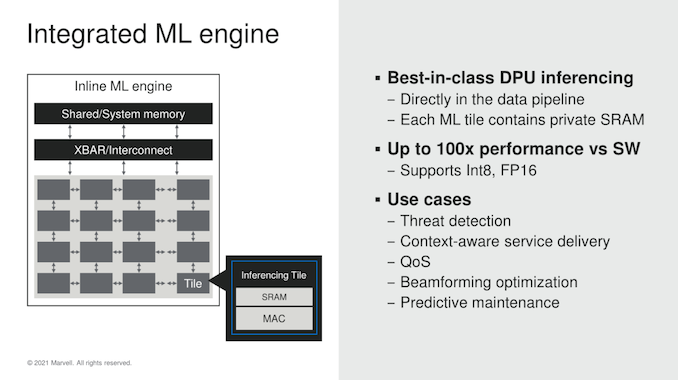

Starting off with what Marvell views as an essential addition to the DPU, is a brand new in-house ML engine. Marvell had said that the design for the IP had truly been initially created for a devoted inference accelerator, and really had been accomplished final 12 months, however with Marvell opting to not carry it to market as a result of extraordinarily crowded aggressive panorama. Instead, Marvell has opted to combine the ML accelerator into their OCTEON DPU chips. Marvell right here states that having the inference accelerator on the identical monolithic silicon chip, immediately built-in into the info pipeline is extraordinarily essential in attaining the low latency for greater throughput processing required for these varieties of knowledge stream use-cases.

Essentially Marvell right here is providing a competitor resolution to Nvidia’s next-gen BlueField-Three DPU when it comes to AI processing capabilities nicely forward when it comes to product technology, as the primary OCTEON 10 options are anticipated to be sampling by finish of this 12 months whereas Nvidia projected BF3 to be arriving in 2022.

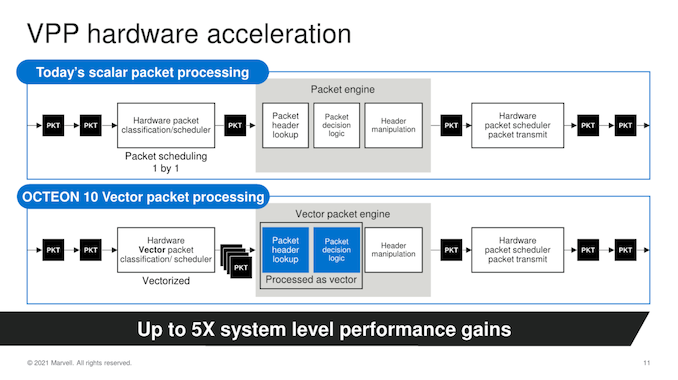

Also, a brand new functionality of the brand new OCTEON 10 household is the introduction of vector packet processing engines, that are capable of vastly increase the packet processing throughput by an element of 5x in comparison with the present technology scalar processing engines.

As famous, the brand new OCTEON 10 DPU household is the primary publicly introduced silicon design that includes Arm’s latest Neoverse N2 infrastructure CPU IP. We had coated the N2 and its HPC V1 sibling a few months in the past – the jist of it’s that the brand new technology core is the primary Armv9 core from Arm and guarantees giant 40% IPC positive aspects compared to the present N1 core seen in Arm server CPUs such because the Amazon Graviton2 or Ampere Altra.

For Marvell, the efficiency enhancements are much more vital as the corporate is switching over from the corporate’s earlier in-house “TX2” CPU IP for the N2 core, promising an enormous 3x greater single-threaded efficiency uplift. Late final 12 months, Marvell had introduced that it had stopped its…

![[CES 2026] A Care Companion for Family Health and Safety –](https://loginby.com/itnews/wp-content/uploads/2026/01/1768059032_CES-2026-A-Care-Companion-for-Family-Health-and-Safety-238x178.jpg)