Kioxia’s sales space at FMS 2024 was a busy one with a number of expertise demonstrations retaining guests occupied. A walk-through of the BiCS eight manufacturing course of was the primary to seize my consideration. Kioxia and Western Digital introduced the sampling of BiCS eight in March 2023. We had touched briefly upon its CMOS Bonded Array (CBA) scheme in our protection of Kioxial’s 2Tb QLC NAND machine and protection of Western Digital’s 128 TB QLC enterprise SSD proof-of-concept demonstration. At Kioxia’s sales space, we received extra insights.

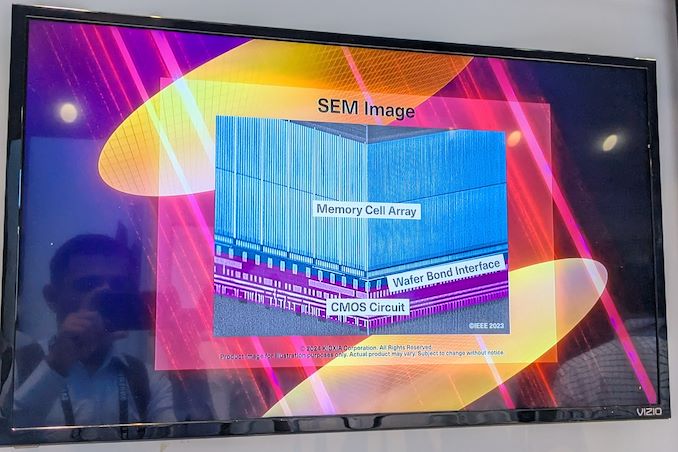

Traditionally, fabrication of flash chips concerned placement of the affiliate logic circuitry (CMOS course of) across the periphery of the flash array. The course of then moved on to placing the CMOS below the cell array, however the wafer growth course of was serialized with the CMOS logic getting fabricated first adopted by the cell array on prime. However, this has some challenges as a result of the cell array requires a high-temperature processing step to make sure greater reliability that may be detrimental to the well being of the CMOS logic. Thanks to latest developments in wafer bonding strategies, the brand new CBA course of permits the CMOS wafer and cell array wafer to be processed independently in parallel after which pieced collectively, as proven within the fashions above.

The BiCS eight 3D NAND incorporates 218 layers, in comparison with 112 layers in BiCS 5 and 162 layers in BiCS 6. The firm determined to skip over BiCS 7 (or, relatively, it was most likely a short-lived era meant as an inside take a look at automobile). The era retains the four-plane cost entice construction of BiCS 6. In its TLC avatar, it’s accessible as a 1 Tbit machine. The QLC model is offered in two capacities – 1 Tbit and a pair of Tbit.

Kioxia additionally famous that whereas the variety of layers (218) does not evaluate favorably with the most recent layer counts from the competitors, its lateral scaling / cell shrinkage has enabled it to be aggressive by way of bit density in addition to working speeds (3200 MT/s). For reference, the most recent transport NAND from Micron – the G9 – has 276 layers with a bit density in TLC mode of 21 Gbit/mm2, and operates at as much as 3600 MT/s. However, its 232L NAND operates solely as much as 2400 MT/s and has a bit density of 14.6 Gbit/mm2.

It should be famous that the CBA hybrid bonding course of has benefits over the present processes utilized by different distributors – together with Micron’s CMOS below array (CuA) and SK hynix’s 4D PUC (periphery-under-chip) developed within the late 2010s. It is anticipated that different NAND distributors may even transfer finally to some variant of the hybrid bonding scheme utilized by Kioxia.