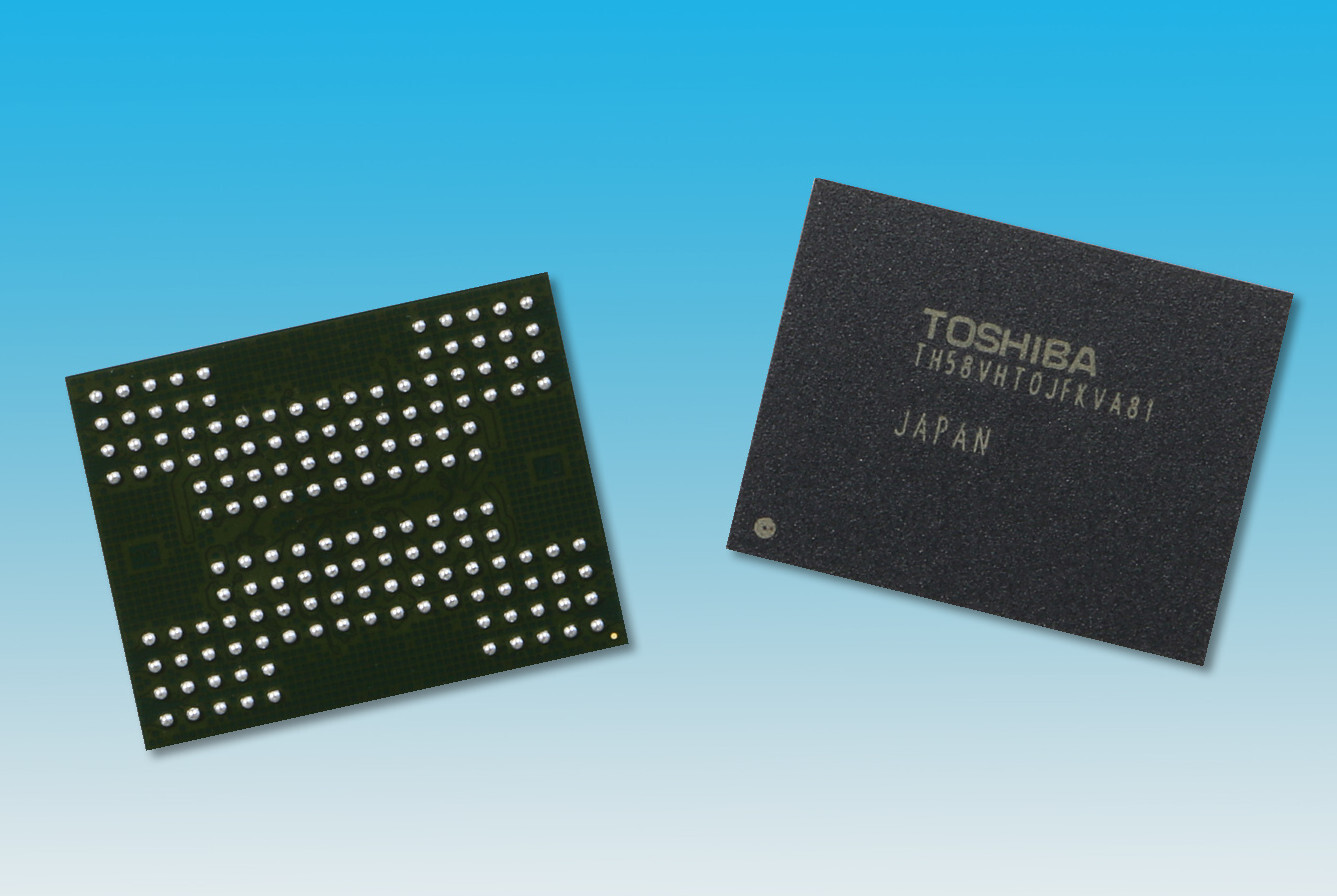

Going ahead, Kioxia will apply its new fifth-generation course of expertise to bigger capability gadgets, equivalent to 1 terabit (128 gigabytes) TLC and 1.33 terabit 4-bit-per-cell (quadruple-level cell, QLC) gadgets.

Kioxia’s progressive 112-layer stacking course of expertise is mixed with superior circuit and manufacturing course of expertise to extend cell array density by roughly 20 p.c over the 96-layer stacking course of. The new expertise reduces the fee per bit and will increase the manufacturability of reminiscence capability per silicon wafer. Additionally, it improves interface velocity by 50 p.c and presents larger programming efficiency and shorter learn latency.

Since asserting the world’s first prototype 3D flash reminiscence expertise in 2007, Kioxia has continued to advance growth of 3D flash reminiscence and is actively selling BiCS FLASH to satisfy the demand for bigger capacities with smaller die sizes.

Fifth-generation BiCS FLASH was developed collectively with expertise and manufacturing accomplice Western Digital Corporation. It can be manufactured at Kioxia’s Yokkaichi Plant and the newly constructed Kitakami Plant.

![[Video] Discover Your Ideal Bespoke AI Laundry Appliance](https://loginby.com/itnews/wp-content/uploads/2026/04/Video-Discover-Your-Ideal-Bespoke-AI-Laundry-Appliance-100x75.jpg)