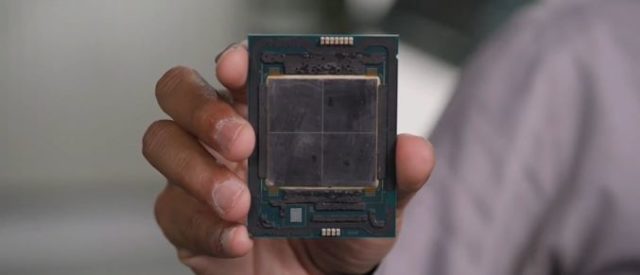

One of the important deficits Intel has to its competitors in its server platform is core depend – different corporations are enabling extra cores by one among two routes: smaller cores, or particular person chiplets linked collectively. At its Architecture Day 2021, Intel has disclosed options about its next-gen Xeon Scalable platform, one among which is the transfer to a tiled structure. Intel is ready to mix 4 tiles/chiplets by way of its quick embedded bridges, main to raised CPU scalability at increased core counts. As a part of the disclosure, Intel additionally expanded on its new Advanced Matrix Extension (AMX) know-how, CXL 1.1 assist, DDR5, PCIe 5.0, and an Accelerator Interfacing Architecture that will result in customized Xeon CPUs sooner or later.

What is Sapphire Rapids?

Built on an Intel 7 course of, Sapphire Rapids (SPR) will likely be Intel’s next-generation Xeon Scalable server processor for its Eagle Stream platform. Using its newest Golden Cove processor cores which we detailed final week, Sapphire Rapids will convey collectively plenty of key applied sciences for Intel: Acceleration Engines, native half-precision FP16 assist, DDR5, 300-Series Optane DC Persistent Memory, PCIe 5.0, CXL 1.1, a wider and sooner UPI, its latest bridging know-how (EMIB), new QoS and telemetry, HBM, and workload specialised acceleration.

Set to launch in 2022, Sapphire Rapids will likely be Intel’s first fashionable CPU product to benefit from a multi-die structure that goals to attenuate latency and maximize bandwidth resulting from its Embedded Multi-Die Interconnect Bridge know-how. This permits for extra high-performance cores (Intel hasn’t mentioned what number of simply fairly but), with the give attention to ‘metrics that matter for its customer base, such as node performance and data center performance’. Intel is looking SPR the ‘Biggest Leap in DC Capabilities in a Decade’.

The headline advantages are straightforward to rattle off. PCIe 5.Zero is an improve over the earlier era Ice Lake PCIe 4.0, and we transfer from six 64-bit reminiscence controllers of DDR4 to eight 64-bit reminiscence controllers of DDR5. But the larger enhancements are within the cores, the accelerators, and the packaging.

Golden Cove: A High-Performance Core with AMX and AIA

By utilizing the identical core design on its enterprise platform Sapphire Rapids and shopper platform Alder Lake, there are a few of the identical synergies we noticed again within the early 2000s when Intel did the identical factor. We lined Golden Cove intimately in our Alder Lake structure deep dive, nevertheless right here’s a fast recap:

The new core, in line with Intel, will over a +19% IPC acquire in single-thread workloads in comparison with Cypress Cove, which was Intel’s backport of Ice Lake. This comes right down to some massive core adjustments, together with:

- 16B → 32B size decode

- 4-wide → 6-wide decode

- 5K → 12Ok department targets

- 2.25Ok → 4K μop cache

- 5 → 6 broad allocation

- 10 → 12 execution ports

- 352 → 512-entry reorder buffer

The objective of any core is to course of extra issues sooner, and the latest era tries to do it higher than earlier than. Plenty of Intel’s adjustments make sense, and people wanting the deeper particulars are inspired to learn our deep dive.

There are some main variations between the buyer model of this core in Alder Lake and the server model in Sapphire Rapids. The most evident one is that the buyer model doesn’t have AVX-512, whereas SPR may have it enabled. SPR additionally has a 2 MB non-public L2 cache per core, whereas the buyer mannequin has 1.25 MB. Beyond this, we’re speaking about Advanced Matrix Extensions (AMX) and a brand new Accelerator Interface Architecture (AIA).

So far in Intel’s CPU cores we now have scalar operation (regular) and vector operation (AVX, AVX2, AVX-512). The subsequent stage up from that could be a devoted matrix solver, or one thing…