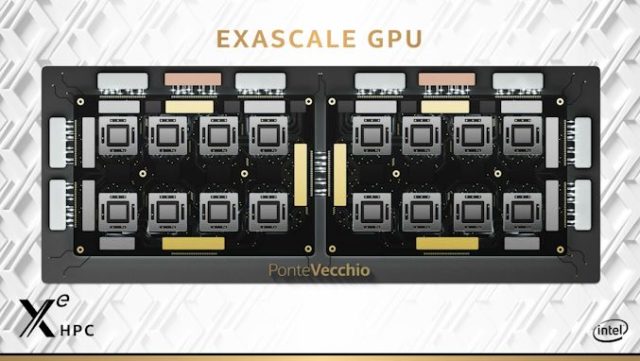

Continuing at this time’s GPU information from Intel’s Architecture Day presentation, on prime of the Xe-LP structure briefing and Xe-HPG reveal, the corporate has additionally supplied a short roadmap replace for his or her flagship sever-level half, Xe-HPC.

Better recognized by its codename of Ponte Vecchio, a lot to do has been made about Xe-HPC. The most advanced of the Xe components deliberate, it’s also the cornerstone of the Intel-powered Aurora supercomputer. Xe-HPC is pulling out the entire stops for efficiency, and to get there Intel is using each trick within the guide, together with their new-generation superior packaging applied sciences.

The large revelation right here is that we lastly have some extra concrete perception into what manufacturing processes the assorted tiles will use. The base tile of the GPU might be on Intel’s new 10nm SuperFin course of, and the Rambo Cache might be a technology newer nonetheless, utilizing Intel’s future 10nm Enhanced SuperFin course of. Meanwhile it’s now confirmed that the Xe Link I/O tile, which might be used as a part of Intel’s material to hyperlink collectively a number of Xe-HPC GPUs, might be constructed by an exterior fab.

That leaves the matter of the compute tile, essentially the most performance-critical of the GPU’s components. With Intel’s 7nm course of delayed by at the very least six months, the corporate has beforehand disclosed that they had been going to take a “pragmatic” method and doubtlessly use third-party fabs. And as of their Architecture Day replace, they nonetheless appear to be undecided about – or at the very least unwilling to reveal – simply what they plan on doing. Instead, the compute die is labeled as “Intel Next Gen & External”.

It’s an uncommon disclosure, to say the least, as we might in any other case anticipate the compute die to be made on a single course of. But with no additional commentary from Intel supplied, make of that what you’ll. Perhaps they’re being simple, and they’ll really use two very completely different course of nodes for the compute die?

![[Video] Discover Your Ideal Bespoke AI Laundry Appliance](https://loginby.com/itnews/wp-content/uploads/2026/04/Video-Discover-Your-Ideal-Bespoke-AI-Laundry-Appliance-100x75.jpg)