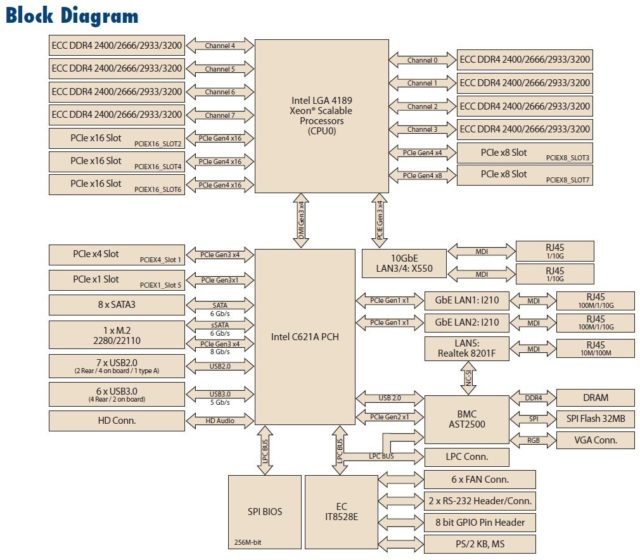

Here’s is the primary schematic of Intel’s upcoming “Whitley” enterprise platform for the upcoming Xeon Scalable “Ice Lake-SP” processors, courtesy momomo_us. The platform sees the introduction of the brand new LGA4189 socket necessitated by Intel growing the reminiscence channels per socket to eight, in comparison with 6 of the current-gen “Cascade Lake-SP.” The new platform additionally sees the introduction of PCI-Express gen 4.zero bus, with every socket placing out as much as 64 PCI-Express gen 4.zero CPU-attached lanes. This are usually wired out as three x16 slots, two x8 slots, an x4 chipset bus, and a CPU-attached 10 GbE controller.

The processor helps as much as eight reminiscence channels working at DDR4-3200 with ECC. The different key element of the platform is the Intel C621A PCH. The C621A talks to the “Ice Lake-SP” processor over a PCI-Express 3.zero x4 hyperlink, and seems to retain gen 3.zero cloth from the older era C621. momomo_us additionally revealed that the 10 nm “Ice Lake-SP” processor might have TDP of as much as 270 W.