This yr, on the worldwide VLSI convention, Intel’s CTO Mike Mayberry gave one of many plenary displays, which this yr was titled ‘The Future of Compute’. Within the presentation, a variety of new manufacturing applied sciences had been mentioned, together with going past FinFET to Gate-All-Around buildings, and even to 2D Nano-sheet buildings, earlier than ultimately doubtlessly leaving CMOS altogether. In the Q&A on the finish of the presentation, Dr. Mayberry said that he expects nanowire transistors to be in excessive quantity manufacturing inside 5 years, placing a really distinctive mark within the sand for Intel and others to succeed in.

Finned transistors, as launched by Intel at ‘22nm’ and everybody else at ‘16nm’, had been a method of scaling the drive present past a planar transistor, a key metric in enabling each density and excessive efficiency logic. Intel is at the moment on its multi-generation FinFET design, with every technology rising the peak of the fins in an effort to assist increase the important thing metrics. As with planar transistors nevertheless, there’s a restrict someplace between a pure restrict and a producing restrict the place one other shift within the transistor design is required. In this case, Gate-All-Around designs, which have been in analysis and improvement for over a decade or extra, or wanted.

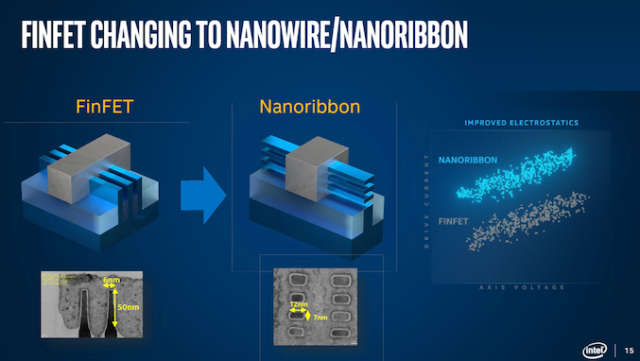

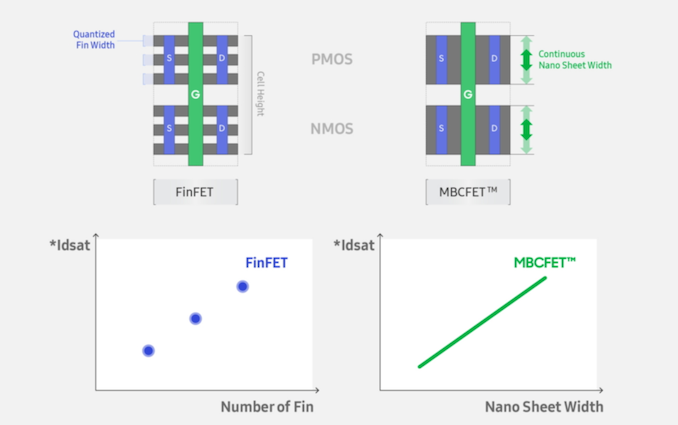

There are a variety of completely different names for Gate-All-Around (GAA) designs. The GAA implementation primarily seems like a hovering transistor fin, which may be both actually small (nanowire) or wider (nanosheet), with a number of stacked wires or sheets rising the efficient width of the transistor in relation to drive present metrics. GAA, for many foundry companies, has anticipated to intersect with the ‘3nm’ node, which ought to supply related density to Intel’s ‘5nm node’.

One of the important thing advantages of those GAA transistors is that the transistor may be particularly tailor-made to the operational necessities. A typical transistor with a FinFET may require a cell peak of 6-7 discrete fins, and thus the drive present is a perform of fin depend. With a GAA sort design, not solely implementing stacking however sheet width as nicely, the drive present is now a steady spectrum, which ought to enable for area financial savings and energy financial savings at a silicon degree. Whereas FinFETs solely have one energy/frequency design level inside a course of node design for a given fin depend, GAA permits a steady scale in transistor design.

Samsung has already introduced its intention to ship GAA transistors into its manufacturing course of on the stage the place it hits a ‘3nm’ course of node. In May 2019, the corporate put out a press launch as a part of its Foundry Forum that the primary beta model of the PDK, v0.1, was prepared for its foundry clients to start out experimenting. At the time, Samsung anticipated the primary trial runs of its 3GAE course of to tapeout in 2020, with danger manufacturing in late 2020, with quantity manufacturing in late 2021.

During the 2020 VLSI Symposia on Technology and Circuits, Intel’s CTO and GM of Technology Development, Dr. Mike Mayberry, gave one of many plenary talks on ‘The Future of Compute’. In the detailed presentation, Dr. Mayberry lined a very good deal about how compute is permeating at each degree, from machine to edge to datacenter, and the way the demand for low-latency and excessive efficiency are key components driving that change. With that comes a variety of design choices and alternatives, but additionally complexity, value, and compute boundaries. One of the necessities to drive paradigm shifts is change on the manufacturing degree, going past FinFET know-how, after we count on each main foundry on the vanguard to start out introducing GAA know-how. Dr. Mayberry lined area particular architectures, reminiscence and…