Notebookcheck has examined an Intel Lakefield Core i5-L16G7 CPU that is being deployed on upcoming Samsung’s Galaxy Book S, and the outcomes are form of a blended bag. For one, Intel’s Lakefield appears to be round 67% slower than the corporate’s earlier ultra-low-power structure, Amber Lake. Something of this might need been attributable to the truth that the Lakefield CPU did not enhance in the direction of its marketed 3.zero GHz; it solely managed to succeed in 2.four GHz, which clearly hampered efficiency. Perhaps pre-release silicon is the perpetrator, or maybe it is the galaxy Book S that is been configured with extra restrictive thermal and energy traits than the chip was truly designed to run at. The chip did handle to run the FireStrike take a look at beating the Amber Lake-based Acer Swift 7 by 23%, although, so not all is trying bleak.

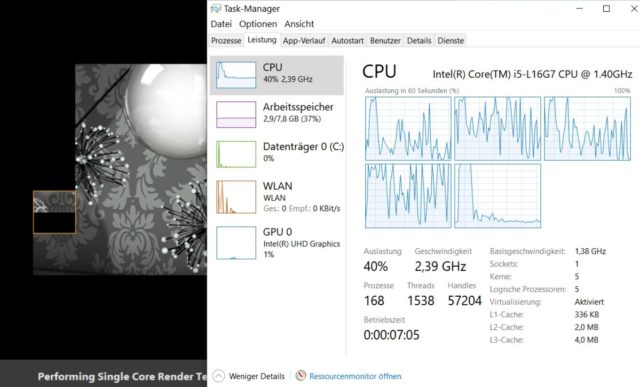

Looking on the screenshots, it does appear that almost all load is being distributed to the low energy Tremond cores, which is clearly the concept in such a low-power design comparable to this (this assumes that the high-performance Sunny Cove core is final on the Task supervisor). It stays to be seen if {hardware} scheduling is being optimum, or if there’s some form of workload shuffle between cores resulting from OS mismanagement of the SoC – it’s a risk, maybe, that the OS is shuffling information between cores, thus affecting efficiency advantages of L1 and L2 caches too aggressively, in an try to maintain hotspot working temperatures in verify.

There is a second within the first benchmark although the place the fifth core sees a surge in workload, transferring as much as 100% utilization, after which declines, giving solution to extra work on two different cores. This appears nicely in keeping with the anticipated use circumstances for the Sunny Cove core and Intel’s ideas on designing these chips: most customers solely require excessive efficiency briefly bursts that want to supply as a lot system responsiveness as attainable, comparable to net web page loading and different comparable workloads.