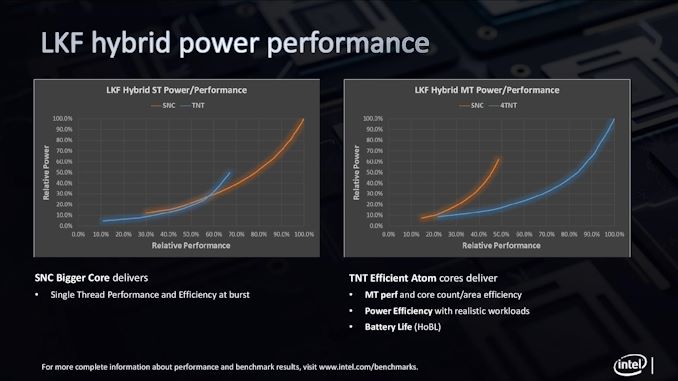

Over the previous 12 months, Intel has slowly began to reveal details about its first hybrid x86 platform, Lakefield. This new processor combines one ‘big’ CPU core with 4 ‘small’ CPU cores, together with a hefty chunk of graphics, with Intel getting down to ship a brand new computing kind issue. Highlights for this processor embrace its small footprint, as a result of new 3D stacking ‘Foveros’ expertise, in addition to its low standby SoC energy, as little as 2.5 mW, which Intel states is 91% decrease than earlier low energy Intel processors. Today’s announcement is available in two elements: first, the specs.

Intel will debut these two SKUs in its first era of Lakefield. These CPUs will discover properties in premium, always-connected laptops, such because the Samsung Galaxy Book S anticipated in markets this month, the Lenovo ThinkPad X1 Fold, coming later this yr, and within the Microsoft Surface Book Neo.

Both SKUs will function one huge ‘Sunny Cove’ CPU core, together with 4 little ‘Tremont’ Atom CPU cores. Both units of cores can have entry to a Four MB final degree cache, though Intel has not but disclosed what kind of cache that is.

Meanwhile on the graphics entrance, Intel is integrating a Gen11 GPU with 64 execution items, the identical variety of EUs as on Intel’s Ice Lake processors. Interestingly, the iGPU is clocked about half as excessive as regular for an Intel GPU, with clockspeeds peaking at simply 500 MHz – suggesting that Intel goes extensive and sluggish to extend graphics efficiency. Both CPUs can be rated for a TDP of seven W.

| Intel Lakefield Processors | ||||||||

| AnandTech | Cores | Base Freq |

1C Turbo |

nT Turbo |

Gen11 IGP |

IGP Freq |

DRAM LP4 |

TDP |

| i5-L16G7 | 1+4 | 1400 | 3000 | 1800 | 64 EUs | 500 | 4267 | 7 W |

| i3-L13G4 | 1+4 | 800 | 2800 | 1300 | 48 EUs | 500 | 4267 | 7 W |

Intel confirmed to us that the bottom frequency is the unified frequency throughout all 5 cores, and the one core turbo frequency applies solely to the massive Sunny Cove core. Support for LPDDR4X-4266 is a notch above the reminiscence controller in Ice Lake, which solely runs at LPDDR4X-3733, and the reminiscence velocity will possible be a giant increase to efficiency.

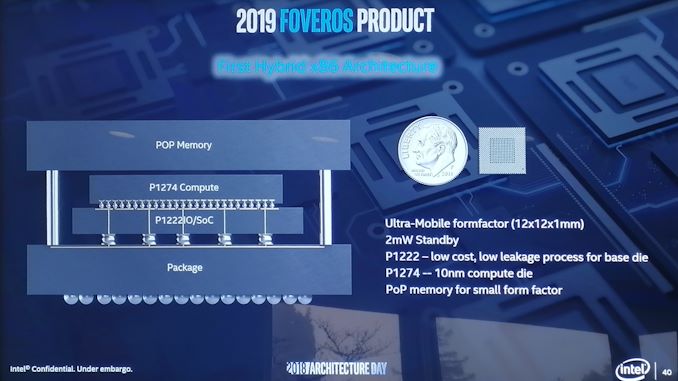

In order to allow these processors in a small 12mm x 12mm footprint, Intel is utilizing its 3D stacking expertise, referred to as Foveros. This signifies that the logic areas of the chip, such because the cores and the graphics, sit on a 10+ nm die, whereas the IO elements of the chip are on a 22nm silicon die, and they’re stacked collectively. In order to make the connections work, Intel has enabled 50 micron connection pads between the 2 silicon halves, together with power-focused TSVs (by silicon vias) to be able to energy the cores on the highest layer.

Intel lists the TDP for these chips at 7 W, though the corporate has not disclosed the turbo energy limits for the chip. As talked about above, Intel hasn’t disclosed how the cache works. In the preliminary diagrams, we had been proven that PoP reminiscence can be added on prime, and whereas Intel hasn’t supplied additional particulars there, we all know from final month’s Samsung Galaxy Book S reveal that there can be (a minimum of) 8GB SKUs utilizing LPDDR4X.

We have huge questions as to how every of the cores will work, on condition that by default they assist completely different instruction units – Intel hasn’t supplied data on this right now. Intel has acknowledged that the scheduling of the threads on the completely different elements of the CPU will happen primarily based on hardware-guided OS scheduling, though once more Intel hasn’t gone into the main points of its {hardware} monitoring and enablement on how that is completed. In the demos we now have seen, Lakefield will use the Tremont cores for nearly all the pieces, and solely name on the Sunny Cove core for user-experience sort of…

![[World Water Day] Samsung’s Promise of Water for All –](https://loginby.com/itnews/wp-content/uploads/2026/03/1774033084_World-Water-Day-Samsung’s-Promise-of-Water-for-All-–-100x75.jpg)