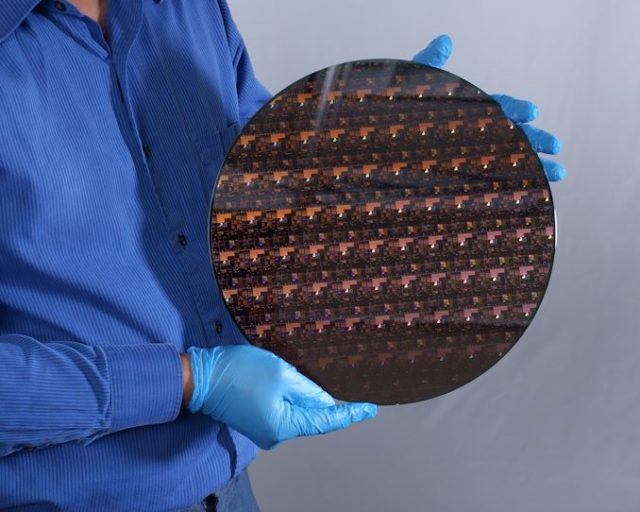

Every decade is the last decade that assessments the boundaries of Moore’s Law, and this decade isn’t any totally different. With the arrival of Extreme Ultra Violet (EUV) know-how, the intricacies of multipatterning strategies developed on earlier know-how nodes can now be utilized with the finer decision that EUV gives. That, together with different extra technical enhancements, can result in a lower in transistor dimension, enabling the way forward for semiconductors. To that finish, Today IBM is asserting it has created the world’s first 2 nanometer node chip.

Names for Nodes

Just to make clear right here, whereas the method node is being known as ‘2 nanometer’, nothing about transistor dimensions resembles a standard expectation of what 2nm could be. In the previous, the dimension was once an equal metric for 2D function dimension on the chip, akin to 90nm, 65nm, and 40nm. However with the appearance of 3D transistor design with FinFETs and others, the method node identify is now an interpretation of an ‘equivalent 2D transistor’ design.

Some of the options on this chip are more likely to be low single digits in precise nanometers, akin to transistor fin leakage safety layers, but it surely’s essential to notice the disconnect in how course of nodes are at the moment named. Often the argument pivots to transistor density as a extra correct metric, and that is one thing that IBM is sharing with us.

Transistor Density

Today’s announcement states that IBM’s 2nm improvement will enhance efficiency by 45% on the similar energy, or 75% vitality on the similar efficiency, in comparison with trendy 7nm processors. IBM is eager to level out that it was the primary analysis establishment to exhibit 7nm in 2015 and 5nm in 2017, the latter of which upgraded from FinFETs to nanosheet applied sciences that enable for a higher customization of the voltage traits of particular person transistors.

IBM states that the know-how can match ’50 billion transistors onto a chip the dimensions of a fingernail’. We reached out to IBM to ask for clarification on what the dimensions of a fingernail was, provided that internally we have been arising with numbers from 50 sq. millimeters to 250 sq. millimeters. IBM’s press relations acknowledged {that a} fingernail on this context is 150 sq. millimeters. That places IBM’s transistor density at 333 million transistors per sq. millimeter (MTr/mm2).

For comparability:

| Peak Quoted Transistor Densities (MTr/mm2) | ||||

| AnandTech | IBM | TSMC | Intel | Samsung |

| 22nm | 16.50 | |||

| 16nm/14nm | 28.88 | 44.67 | 33.32 | |

| 10nm | 52.51 | 100.76 | 51.82 | |

| 7nm | 91.20 | 237.18* | 95.08 | |

| 5nm | 171.30 | |||

| 3nm | 292.21* | |||

| 2nm | 333.33 | |||

| Data from Wikichip, Different Fabs might have totally different counting methodologies * Estimated Logic Density |

||||

As you’ll be able to inform, totally different foundries have totally different official names with a wide range of densities. It’s value noting that these density numbers are sometimes listed as peak densities, for transistor libraries the place die space is the height concern, relatively than frequency scaling – usually the quickest elements of a processor are half as dense as these numbers because of energy and thermal issues.

With regards the motion to Gate-All-Around / nanosheet transistors, whereas not explicitly acknowledged by IBM, photographs present that this new 2nm processor is utilizing a three-stack GAA design. Samsung is introducing GAA at 3nm, whereas TSMC is ready till 2nm. Intel in contrast, we consider, will introduce some type of GAA on its 5nm course of.

IBM’s 3-stack GAA makes use of a cell top of 75 nm, a cell width of 40 nm, and the person nanosheets are 5nm in top, separated from one another by 5 nm. The gate poly pitch is 44nm, and…