08:22PM EDT – Welcome to Hot Chips! This is the annual convention all in regards to the newest, biggest, and upcoming massive silicon that will get us all excited. Stay tuned throughout Monday and Tuesday for our common AnandTech Live Blogs.

08:22PM EDT – Going to begin right here in about 10 minutes

08:30PM EDT – Should nearly to begin

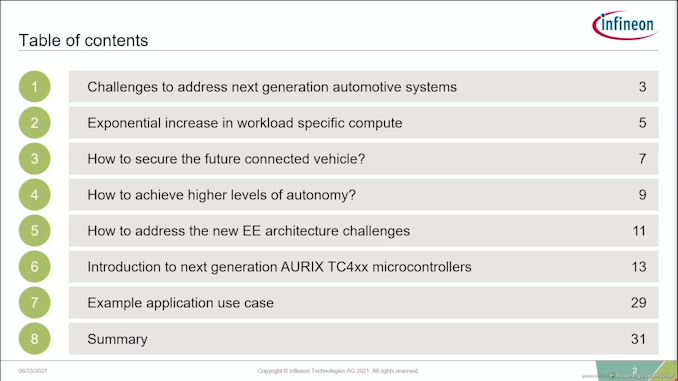

08:32PM EDT – First up is Infineon

08:32PM EDT – Next gen automotive challenges

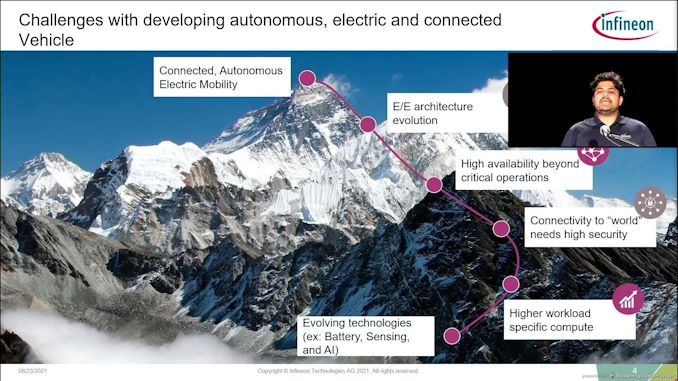

08:33PM EDT – Let’s go climb a mountain

08:33PM EDT – Literally drive up a mountain!

08:34PM EDT – Evolving applied sciences – Battery, Sensing, AI

08:35PM EDT – Adaptable architectures with excessive availability with none legacy impression

08:35PM EDT – Machine Learning – workload particular compute

08:35PM EDT – quick safety accelerators for authentification

08:36PM EDT – E-architecture evolution

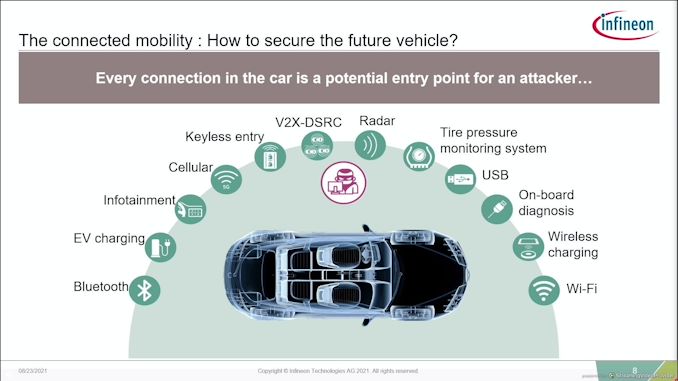

08:36PM EDT – Connectivity – logical assaults, spoofing – any connection out is an assault vector

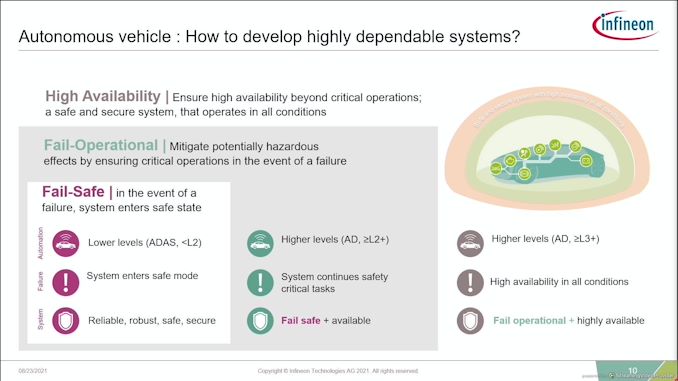

08:36PM EDT – Need fail-safe system

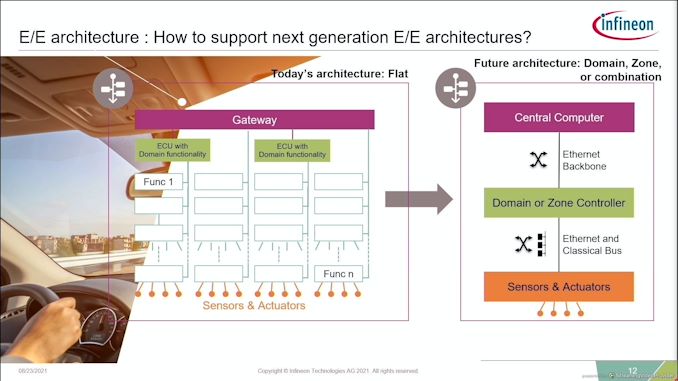

08:38PM EDT – Moving in direction of future architectures with an ethernet spine and a central pc

08:38PM EDT – ALso helps lowering price

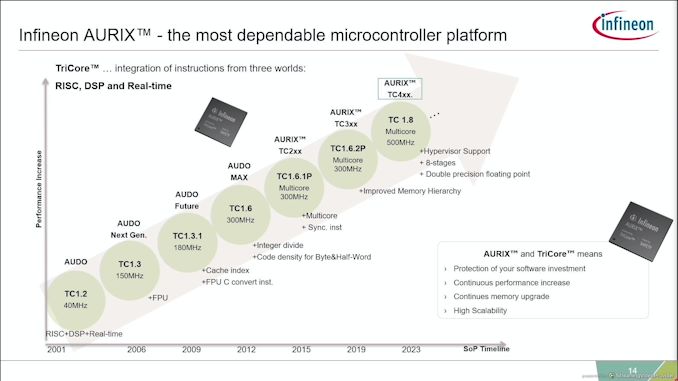

08:38PM EDT – Infineon Aurix and Tricore structure

08:38PM EDT – Designed round 20 years in the past – Tricore

08:38PM EDT – Aurix in manufacturing since 2015, Tricore since 1995

08:39PM EDT – Adding fashionable options as time goes on

08:39PM EDT – 500 MHz in newest gen

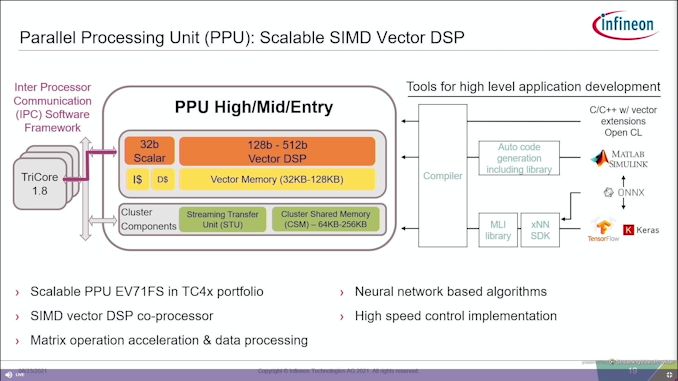

08:39PM EDT – new accelerators – parallel processing, enhanced DSPs

08:40PM EDT – ASIL D security, safety requirements

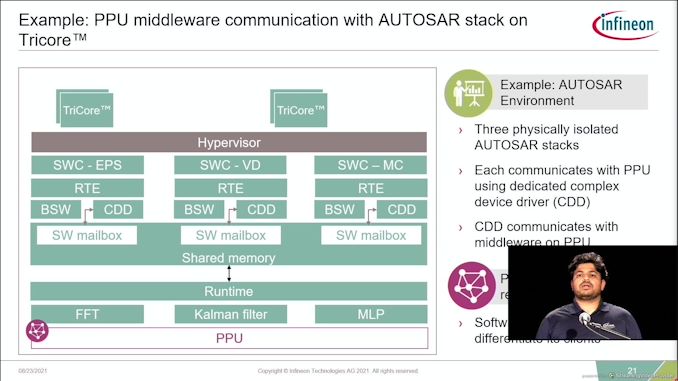

08:40PM EDT – Hardware isolation on the core degree, eight VMs per core and Hypervisor

08:40PM EDT – Fine granular entry safety, DMA safety

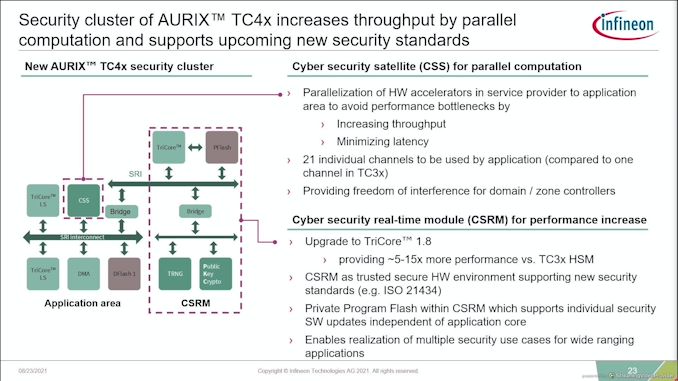

08:41PM EDT – 2 x 5 Gbit ethernet, accelerated MACsec assist, {hardware} acceleration for encryption

08:41PM EDT – two PCIe 3.zero x1 lanes

08:42PM EDT – Full CPU architectgure structure

08:42PM EDT – six cores at 500 MHz

08:42PM EDT – Debug and Trace

08:42PM EDT – SIMD Vector DSP and Scalar core

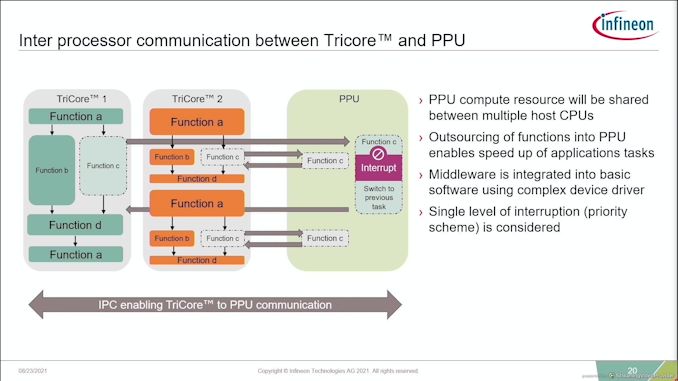

08:42PM EDT – ARC EV71FS Parallel Processing Unit

08:43PM EDT – Software stack

08:44PM EDT – Security – Security cluster

08:57PM EDT – Supports automotive encryption, intrusion detection, bodily or digital

08:57PM EDT – Sorry, Internet reduce out for 10 minutes, ISP went borked

08:58PM EDT – Just within the Q&A bit now of this discuss. Going to chop losses, and simply await the following discuss in 2 minutes

09:02PM EDT – Second discuss is EdgeQ – Open RISC-V 5G Radio Access Networks

09:03PM EDT – One of the rising corporations

09:04PM EDT – First software program programmable SoC for AI and 5G

09:04PM EDT – 5G basestation on a single chip

09:04PM EDT – 50+ SoCs launched, 2 billion modems shipped, $100b income generated

09:05PM EDT – Was in stealth till finish of final yr

09:05PM EDT – Next Generation RAN

09:06PM EDT – Banding for 5G is vital

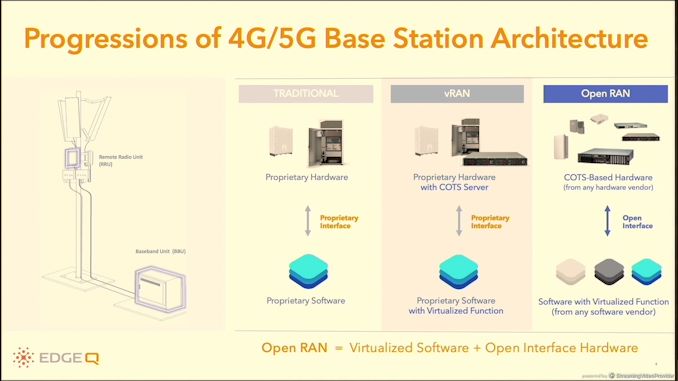

09:06PM EDT – Progression of 5G RAN over time

09:07PM EDT – OpenRAN utilizing Off-the-shelf {hardware}

09:07PM EDT – Migration to a cloud native mannequin

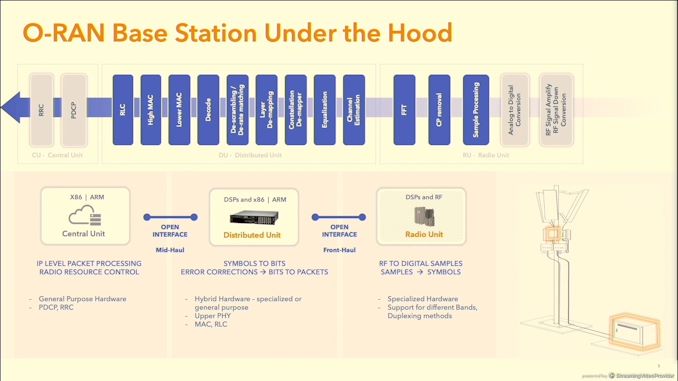

09:08PM EDT – Central Unit, Distributed Unit, Radio Unit

09:08PM EDT – Signal processing

09:09PM EDT – Requires scheduling of customers

09:09PM EDT – Multiple RUs to at least one central unit

09:10PM EDT – DU is a hybrid structure – blended particular {hardware} or normal {hardware}

09:10PM EDT – What’s wanted is the open interfaces between every part

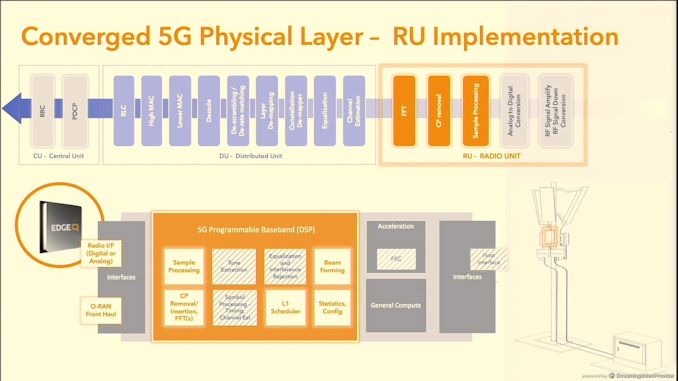

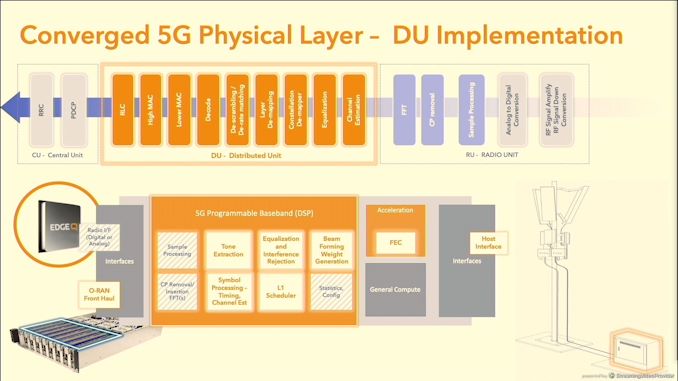

09:11PM EDT – 5G programmable baseband DSP

09:12PM EDT – one EdgeQ is within the Radio Unit

09:12PM EDT – Distributed Unit has a number of EdgeQ chips for sign processing

09:13PM EDT – Developing a converged SoC

09:13PM EDT – Need a programmable DSP engine

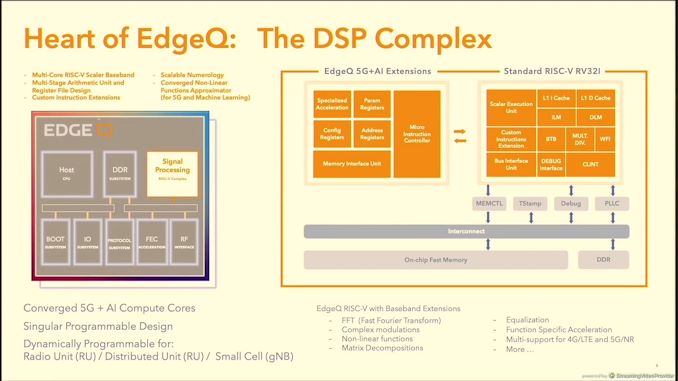

09:14PM EDT – RISC-V with 50+ customized directions

09:14PM EDT – eight-core Arm Neoverse CPU subsystem

09:14PM EDT – Accelerators, IO subsystem, PCIe, USB, Ethernet

09:14PM EDT – GNU Tool Chain

09:14PM EDT – Massively parallel

09:17PM EDT – Supports a number of configurations and is software program upgradeable

09:17PM EDT – beamforming, different intense operations

09:18PM EDT – gang as much as four chips for as much as 40…