03:26PM EDT – a couple of minute till the Synopsys keynote begins

03:28PM EDT – Today’s Keynote Speaker is CEO Aart de Geus about Machine Learning in EDA instruments

03:28PM EDT – Here’s a preview

03:28PM EDT – https://www.anandtech.com/show/16784/using-ai-to-build-processors-google-was-just-the-start-says-synopsys

03:32PM EDT – ‘If you recognize chips, you recognize Synopsys’

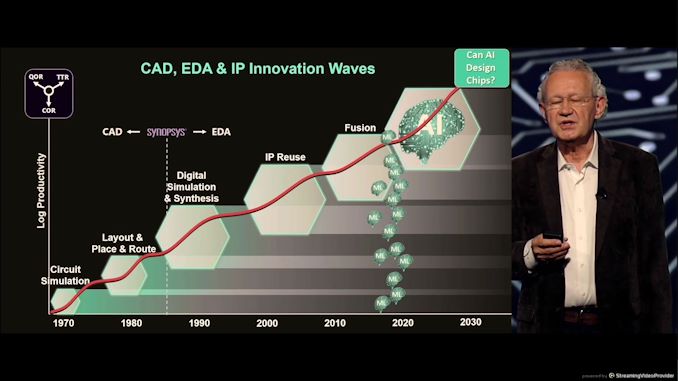

03:33PM EDT – At the middle of each advance in EDA since

03:33PM EDT – Undergrad in Switzerland

03:34PM EDT – Being capable of see the world in several views

03:34PM EDT – Hot Chips is the place you discover the perfect architects

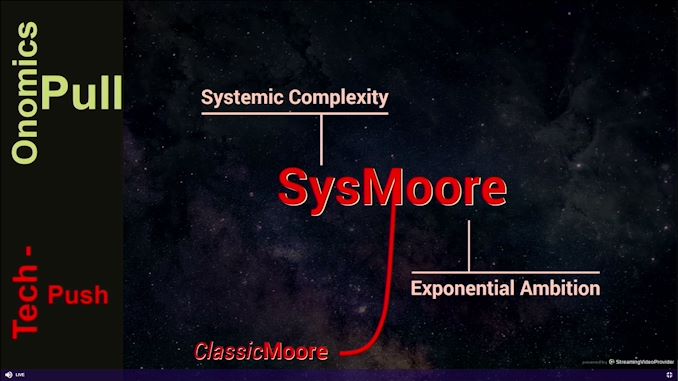

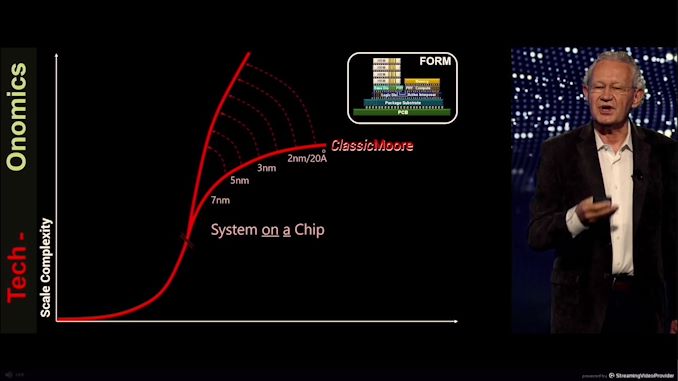

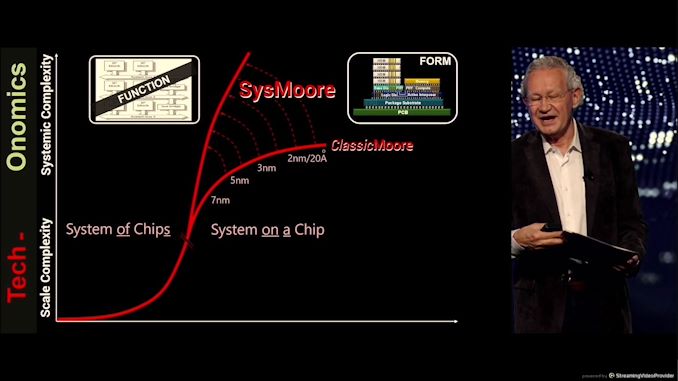

03:35PM EDT – New SysMoore Era

03:35PM EDT – The mission for the following 20 years – architecting intellegence

03:35PM EDT – Architecting of smarts

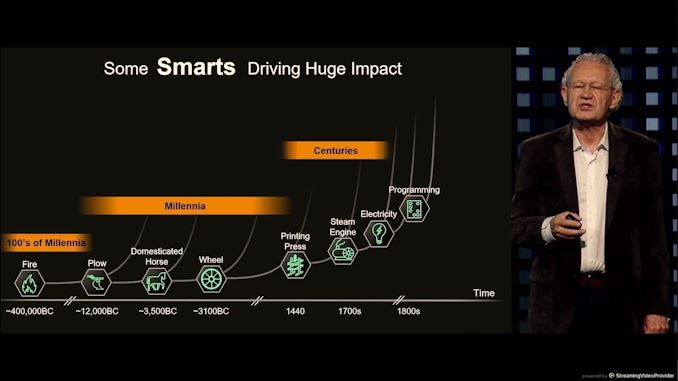

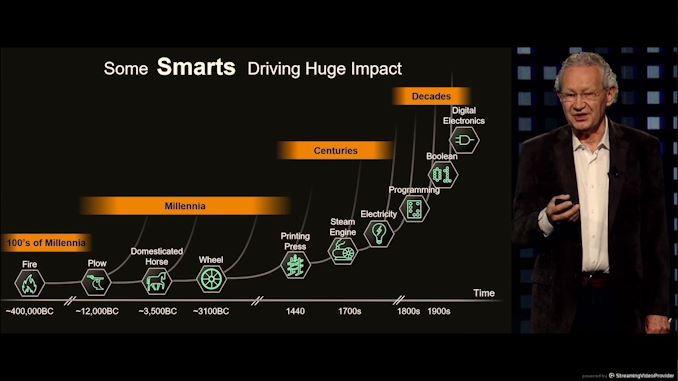

03:35PM EDT – Smart drive impactg

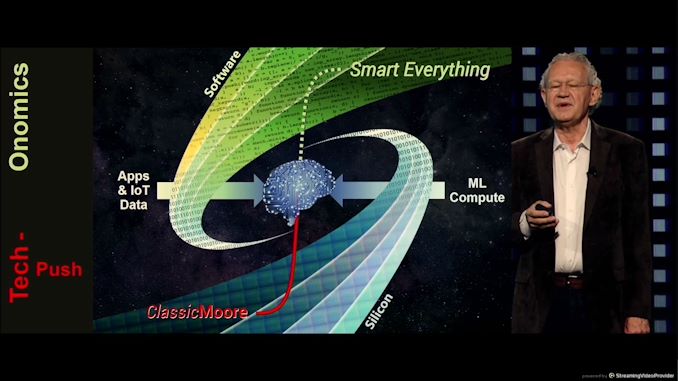

03:36PM EDT – Smart Everything

03:36PM EDT – Ideas and engineering -duct tape and WD40

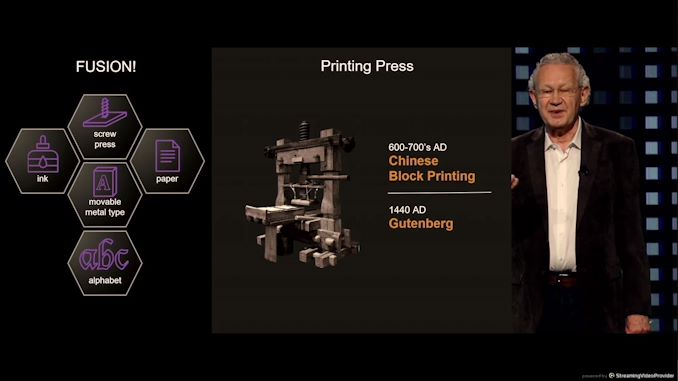

03:37PM EDT – Impact of printing press – 20m books after printed press was ‘redescovered’

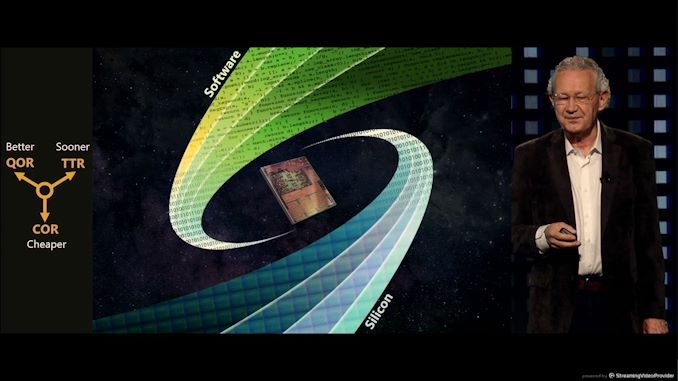

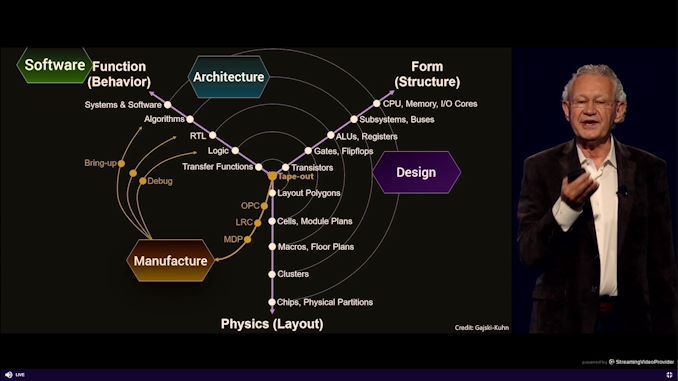

03:38PM EDT – Software and Silicon

03:39PM EDT – Add in Thermal results

03:39PM EDT – Solving systemic points, safety, silicon life cycle, performance

03:39PM EDT – balancing all the necessities

03:39PM EDT – Applying the imaginative and prescient with optionality within the center

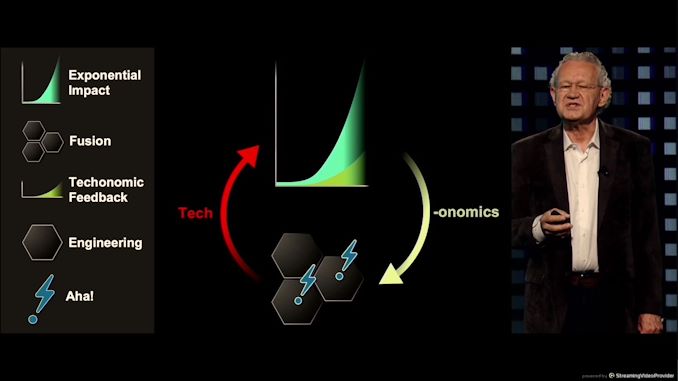

03:39PM EDT – Techonomics

03:40PM EDT – ML algorithms should be computing in time

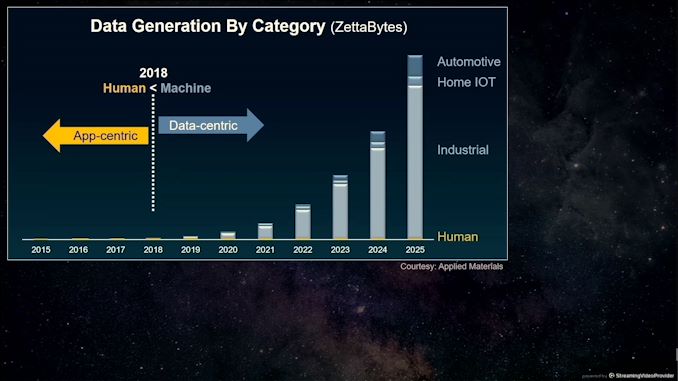

03:40PM EDT – Growth within the quantity of knowledge

03:40PM EDT – ‘Can we do this AI factor’

03:41PM EDT – Data generated by people is minmal

03:41PM EDT – in contrast what’s generated by machines

03:42PM EDT – Using AI to be more practical with system requests and necessities

03:42PM EDT – Systemic Complexity vs Exponential Ambition = Sysmoore

03:43PM EDT – Systemic complexity vs scale complexity – we have solved scale complexity

03:44PM EDT – changing no as a result of with sure if

03:44PM EDT – Moore’s Law does not at all times imply smaller gadgets

03:45PM EDT – Angrsrom has the phrase Angst in it!

03:45PM EDT – A booster pack to Moore’s Law

03:45PM EDT – System of Chips

03:45PM EDT – AI is driving a rethink in architectures

03:45PM EDT – Function and type

03:46PM EDT – Form should comply with operate

03:48PM EDT – Sorry the animations right here hold overwriting one another

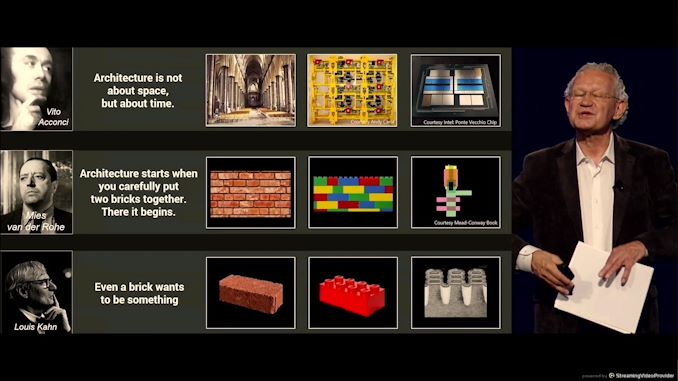

03:48PM EDT – Talking about structure and growth

03:49PM EDT – blocks vs building vs time – all in regards to the subsequent stage of abstraction

03:49PM EDT – Levels of abstraction

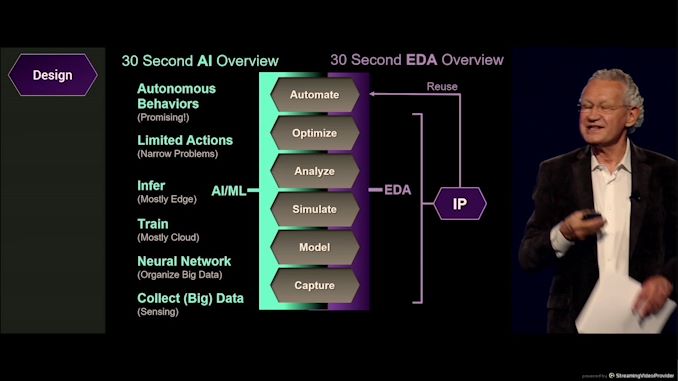

03:51PM EDT – Now time for EDA

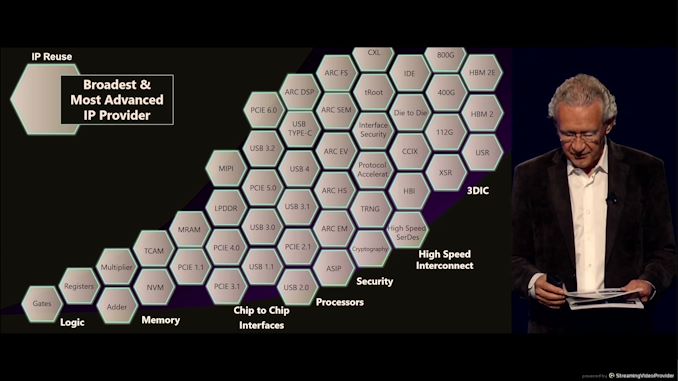

03:51PM EDT – IP reuse

03:51PM EDT – Integrating ML into EDA

03:52PM EDT – Now for circuit simulation

03:54PM EDT – Developing AI for EDA

03:54PM EDT – Using AI to do extra

03:54PM EDT – AI allows higher automation – EDA already has a lot of automation

03:54PM EDT – Arm enabled IP reuse

03:55PM EDT – wanting {hardware} at latency and capability of communication

03:55PM EDT – 4nm in manufacturing at the moment

03:56PM EDT – Fusion compiler – 500 instances

03:56PM EDT – Everyone of Synopsys instruments has some type of machine studying

03:57PM EDT – Can you allow ML on design circulation

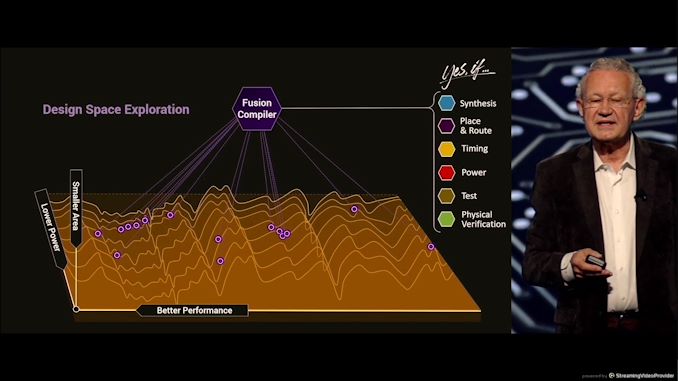

03:57PM EDT – Using you allow autonomous design? YES

03:58PM EDT – But it will get more durable with AI

03:58PM EDT – Moving type win/lose to higher/worse

04:00PM EDT – Design Space Optimization, not simply exploration

04:00PM EDT – utilizing every part they’ve discovered up to now

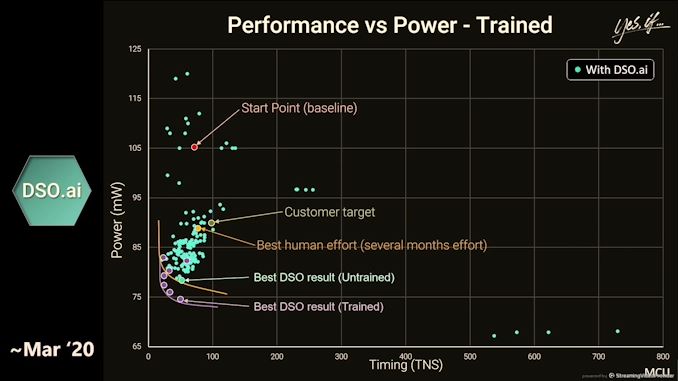

04:00PM EDT – outcomes from actual designs

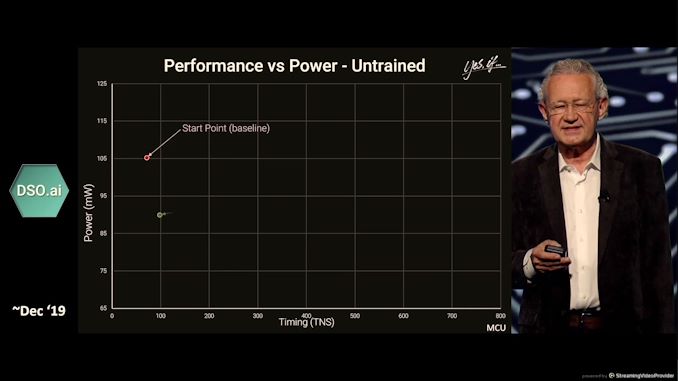

04:00PM EDT – This is in december 19

04:01PM EDT – Best result’s nicely above any human design

04:01PM EDT – Tested 10-100x greater than a human design crew

04:02PM EDT – This is untrained

04:02PM EDT – Using a educated model

04:03PM EDT – Here’s one other instance of a buyer outcome

04:04PM EDT – Single engineer vs a crew

04:04PM EDT – A 3rd instance

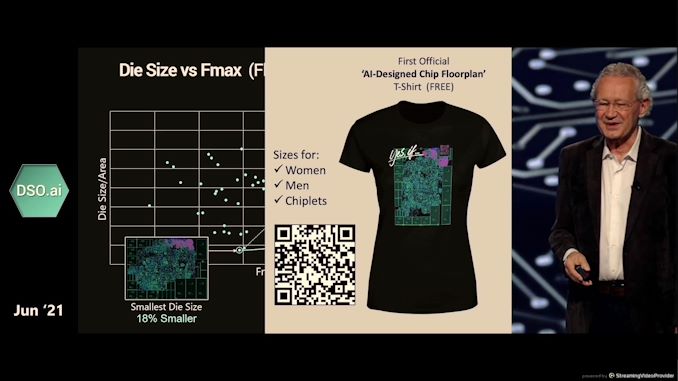

04:05PM EDT – Learning from closing outcomes

04:07PM EDT – Free t-shirt on the QR code

04:07PM EDT – with the diagram in

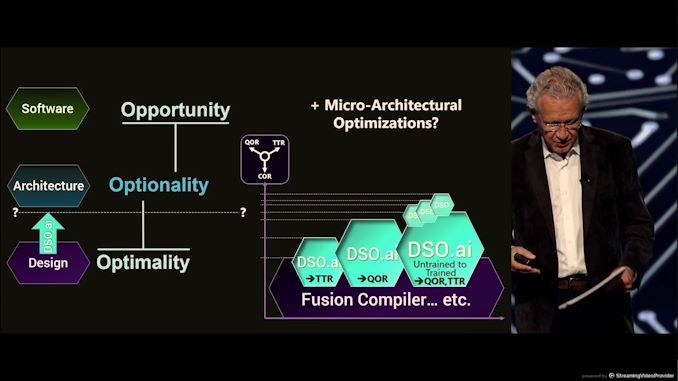

04:07PM EDT – Using DSO.ai on the microarchitecture stage

04:08PM EDT – Can you get AI to make microarch changes?

04:08PM EDT – Architecture searches

04:08PM EDT – with…