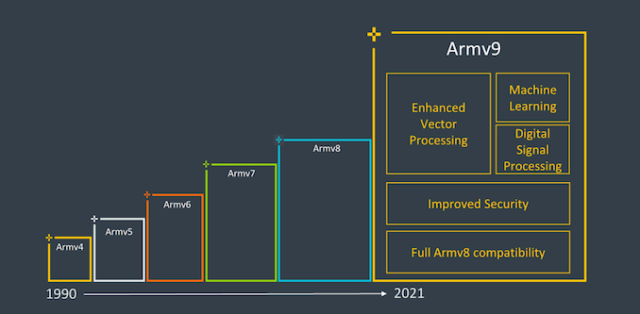

It’s been practically 10 years since Arm had first introduced the Armv8 structure in October 2011, and it’s been a fairly eventful decade of computing because the instruction set structure noticed elevated adoption by means of the cellular area to the server area, and now beginning to develop into frequent within the shopper units market equivalent to laptops and upcoming desktop machines. Throughout the years, Arm has advanced the ISA with varied updates and extensions to the structure, some vital, some possibly glanced over simply.

Today, as a part of Arm’s Vision Day occasion, the corporate is asserting the primary particulars of the corporate’s new Armv9 structure, setting the inspiration for what Arm hopes to be the computing platform for the subsequent 300 billion chips within the subsequent decade.

The huge query that readers will seemingly be asking themselves is what precisely differentiates Armv9 to Armv8 to warrant such a big soar within the ISA nomenclature. Truthfully, from a purely ISA standpoint, v9 in all probability isn’t an as elementary soar as v8 was over v7, which had launched a totally totally different execution mode and instruction set with AArch64, which had bigger microarchitectural ramifications over AArch32 equivalent to prolonged registers, 64-bit digital deal with areas and lots of extra enhancements.

Armv9 continues the utilization of AArch64 because the baseline instruction set, nevertheless provides in a number of essential extensions in its capabilities that warrants an increment within the structure numbering, and doubtless permits Arm to additionally obtain a kind of software program re-baselining of not solely the brand new v9 options, but additionally the varied v8 extensions we’ve seen launched over time.

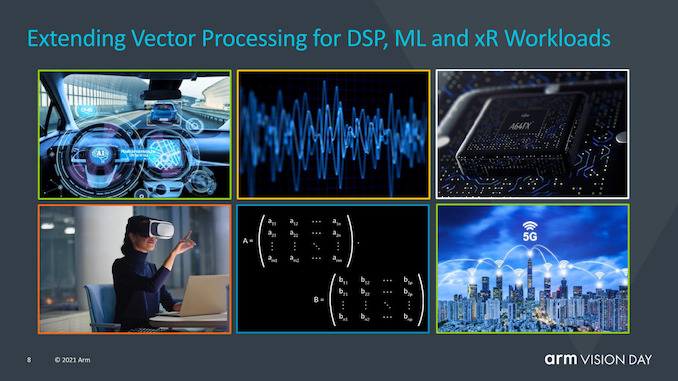

The three new fundamental pillars of Armv9 that Arm sees as the principle targets of the brand new structure are safety, AI, and improved vector and DSP capabilities. Security is a really huge subject for v9 and we’ll go into the brand new particulars of the brand new extensions and options into extra depth in a bit, however getting DSP and AI options out of the way in which first needs to be easy.

Probably the largest new characteristic that’s promised with new Armv9 suitable CPUs that can be instantly seen to builders and customers is the baselining of SVE2 as a successor to NEON.

Scalable Vector Extensions, or SVE, in its first implementation was introduced again in 2016 and carried out for the primary time in Fujitsu’s A64FX CPU cores, now powering the world’s #1 supercomputer Fukagu in Japan. The drawback with SVE was that this primary iteration of the brand new variable vector size SIMD instruction set was somewhat restricted in scope, and aimed extra at HPC workloads, lacking lots of the extra versatile directions which nonetheless have been lined by NEON.

SVE2 was introduced again in April 2019, and appeared to unravel this challenge by complementing the brand new scalable SIMD instruction set with the wanted directions to serve extra various DSP-like workloads that at the moment nonetheless use NEON.

The good thing about SVE and SVE2 past addition varied fashionable SIMD capabilities is of their variable vector dimension, starting from 128b to 2048b, permitting variable 128b granularity of vectors, no matter what the precise {hardware} is operating on. Purely from a view of vector processing and programming, it implies that a software program developer would solely ever must compile his code as soon as, and if sooner or later a CPU would come out with say native 512b SIMD execution pipelines, the code would be capable to already benefit from the complete width of the items. Similarly, the identical code would be capable to run on extra conservative designs with a decrease {hardware} execution width functionality, which is vital to Arm as they design CPUs from IoT, to cellular, to datacentres. It additionally does this all while remaining throughout the 32b encoding area of the Arm structure, whereas…