Although the tempo of Moore’s Law has undeniably slackened within the final decade, transistor density continues to be growing with each new course of expertise. But there’s a problem with feeding energy to smaller transistors, as with the smaller transistors comes thinner energy wires inside the chip, which will increase their resistance and will trigger yield loss. Looking to fight that impact, this week Applied Materials launched its new Applied Endura Copper Barrier Seed IMS with Volta Ruthenium Copper Vapor Deposition (CVD) instrument, which allows chipmakers to maintain utilizing copper for wiring with 2 nm-class and extra superior course of applied sciences.

Today’s superior logic processors have about 20 layers of metallic, with skinny sign wires and thicker energy wires. Scaling down wiring with shrinking transistors presents quite a few challenges. Thinner wires have larger electrical resistance, whereas nearer wires heighten capacitance and electrical crosstalk. The mixture of the 2 can result in elevated energy consumption whereas additionally limiting efficiency scaling, which is especially problematic for datacenter grade processors that need to have all of it. Moving energy rails to a wafer’s back-side is anticipated to reinforce efficiency and effectivity by lowering wiring complexity and releasing up area for extra transistors.

But bottom energy supply community (BSPDN) doesn’t clear up the issue with skinny wires typically. As lithographic scaling progresses, each transistor options and wiring trenches grow to be smaller. This discount implies that obstacles and liners take up extra space in these trenches, leaving inadequate room to deposit copper with out creating voids, which raises resistance and may decrease yields. Additionally, the nearer proximity of wires thins the low-k dielectrics, making them extra weak to break through the etching course of. This injury will increase capacitance and weakens the chips, making them unsuitable for 3D stacking. Consequently, because the trade advances, copper wiring faces vital bodily scaling challenges. But Applied Materials has an answer.

Adopting Binary RuCo Liners

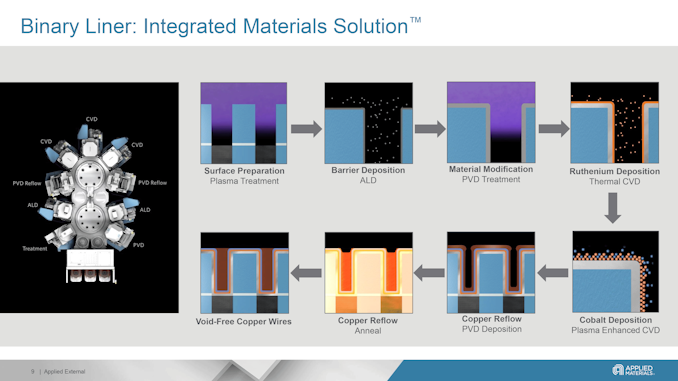

Contemporary manufacturing applied sciences use reflow to fill interconnects with copper, the place anneals assist the copper circulate from the wafer floor into wiring trenches and vias. This course of relies on the liners on which the copper flows. Normally, a CVD cobalt movie was used for liners, however this movie is simply too thick for 3nm-class nodes (which might have an effect on resistance and yield).

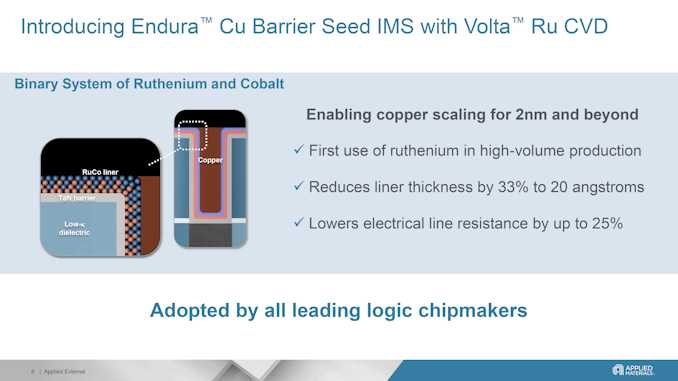

Applied Materials proposes utilizing a ruthenium cobalt (RuCo) binary liner with a thickness beneath 20A (2nm, 20 angstroms), which would supply higher floor properties for copper reflow. This would finally permit for 33% extra space for void-free conductive copper to be reflowed, lowering the general resistance by 25%. While utilization of the brand new liner requires new tooling, it might allow higher interconnects that imply larger efficiency, decrease energy consumption and better yields.

Applied Materials says that thus far its new Endura Copper Barrier Seed IMS with Volta Ruthenium CVD instrument has been adopted by all main logic makers, together with TSMC and Samsung Foundry for his or her 3nm-class nodes and past.

“The semiconductor industry must deliver dramatic improvements in energy-efficient performance to enable sustainable growth in AI computing,” mentioned Dr. Y.J. Mii, Executive Vice President and Co-Chief Operating Officer at TSMC. “New materials that reduce interconnect resistance will play an important role in the semiconductor industry, alongside other innovations to improve overall system performance and power.”

New Low-Ok Dielectric

But skinny and environment friendly liner will not be the one factor essential for wiring at 3nm manufacturing nodes and past. Trenches for wiring are filed…