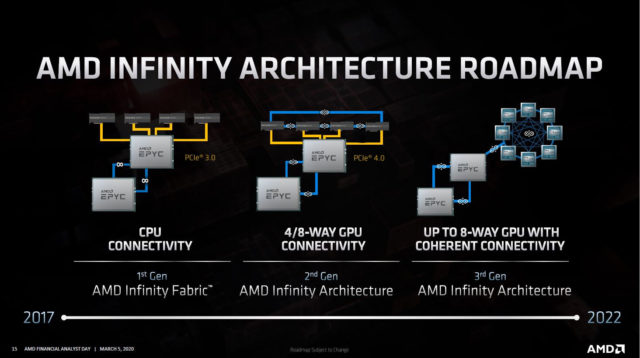

For starters, “Zen 4” continues on AMD’s trajectory of including IPC beneficial properties with every era. Secondly, “Zen 4” will leverage the superior 5 nm silicon fabrication course of, which ought to considerably improve transistor densities over even essentially the most superior iterations of seven nm, equivalent to 7 nm EUV. “Zen 4” comes out roughly the identical time because the RDNA3 and CDNA2 graphics architectures, and AMD’s third era Infinity Fabric interconnect that permits exascale supercomputers because of coherent unified reminiscence and huge shared reminiscence swimming pools between CPUs and compute GPUs. Elsewhere within the roadmap, we see AMD asserting that its upcoming “Zen 3” microarchitecture and its enterprise implementation, the EPYC “Milan” processor, will launch solely towards the tip of 2020. This would give EPYC “Rome” shut to six calendar quarters of market management.

Although not in reference to “Genoa,” AMD briefly talked in regards to the subsequent step in its package deal improvements which have helped it overcome the results of a slowdown in Moore’s Law cadence. The firm carried out MCMs for its first-generation “Naples,” and transcended to the chiplet method with second era “Rome,” through which solely these elements that profit from the change to a brand new node can be constructed on the brand new node, whereas uncore and I/O elements can be constructed on separate dies and older course of nodes, which is basically anticipated to hold ahead with “Milan.” Some time sooner or later, by way of, the corporate may embrace an X3D “2.5D + 3D” package deal design that sees the mix of 3D reminiscence stacks sitting alongside 2.5D logic stacks.