One of the tales effervescent away within the background of the trade is the AMD self-imposed ‘25×20’ objective. Starting with efficiency in 2014, AMD dedicated to itself, to clients, and to buyers that it might obtain an total 25x enchancment in ‘Performance Efficiency’ by 2020, which is a perform of uncooked efficiency and energy consumption. At the time AMD was defining its Kaveri cell product because the baseline for the problem – admittedly a really low bar – nevertheless annually AMD has up to date us on its progress. With this yr being 2020, the query on my lips ever for the reason that launch of Zen2 for cell was if AMD had achieved its objective, and in that case, by how a lot? The reply is sure, and by rather a lot.

In this text we’ll recap the 25×20 venture, how the metrics are calculated, and what this implies for AMD in the long run.

Renoir 2020: New Silicon, Goal Achieved

The announcement as we speak from AMD confirms the corporate has reached its objective of 25x efficiency effectivity by the top of 2020, ranging from the Kaveri baseline. Here’s the vital graph:

As we are able to see utilizing this metric, there have been massive jumps from Kaveri to Carrizo, Bristol Ridge to Raven Ridge, then a sequence of stagnation over Zen/Zen+, earlier than lastly a bump as much as Renoir. This offers three distinct jumps:

- Kaveri to Carrizo was 3.5x,

- Bristol to Raven was 2.2x,

- then Picasso to Renoir was 2.92x

The base worth for AMD’s objective is on its Kaveri cell processors, which by the requirements of as we speak set a really low bar. As AMD moved to Carrizo, it carried out new energy monitoring options on chip that allowed the system to supply a greater distribution of energy and ran nearer to the true voltage wanted, not losing energy. After Carrizo got here Bristol Ridge, nonetheless primarily based on the older cores, however used a brand new DDR4 controller in addition to decrease powered processors that had been higher optimized for effectivity.

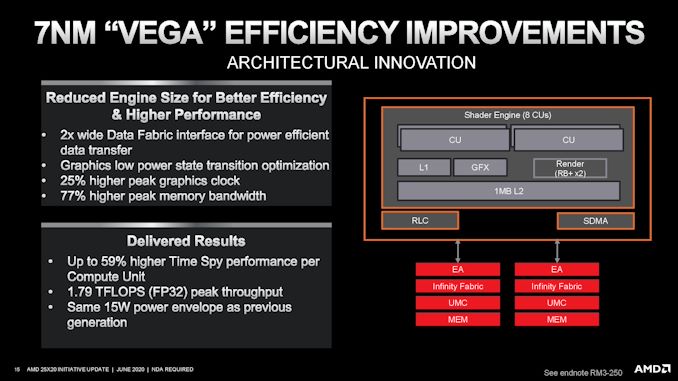

A giant leap got here with Raven Ridge, with AMD combining its new extremely environment friendly Zen x86 cores and Vega built-in graphics. This heralded an enormous enchancment in efficiency resulting from doubling the cores and bettering the graphics, all inside the same energy window as Bristol Ridge. This boosted up the vital 25×20 metric and holding it effectively above the ‘linear’ achieve.

From 2017-2019, this was finally a lull in AMD’s technique, particularly as a result of there have been no vital design modifications. The variations of 2017/2018 Raven Ridge come all the way down to slight SKU variations used for the metric, however finally when it got here time to measure the techniques AMD was just a little out of cycle right here. Moving from Raven Ridge to Picasso was a shift from utilizing GlobalFoundries 14nm to 12nm, which affords a slight energy achieve however not a lot on the efficiency. Going from 2017 to 2019 nonetheless yielded a 23.5% achieve throughout the similar product household, primarily resulting from minor manufacturing updates and higher binning or energy algorithms. It was across the Picasso time when OEM’s began taking AMD’s pocket book platform extra critically, particularly because the lead as much as 2020’s Renoir.

The bounce from Picasso to Renoir has been effectively documented. Our first use of the CPUs, reviewed within the ASUS Zephyrus G14, left us with our mouths open, nearly actually. We referred to as it a ‘Mobile Revival’, showcasing AMD’s transition over from Zen+ to Zen2, from GF 12nm to TSMC 7nm, together with lots of robust design and optimization on the graphics aspect. The modifications from the 2019 to the 2020 chip embody doubling the core depend, from 4 to eight, bettering the clock-for-clock efficiency by 15-20%, but additionally bettering the graphics efficiency and frequencies regardless of shifting down from an silicon design that had 11 compute models down to eight. This comes in keeping with a lot of energy updates, adhering to AHCI specs, and as we…