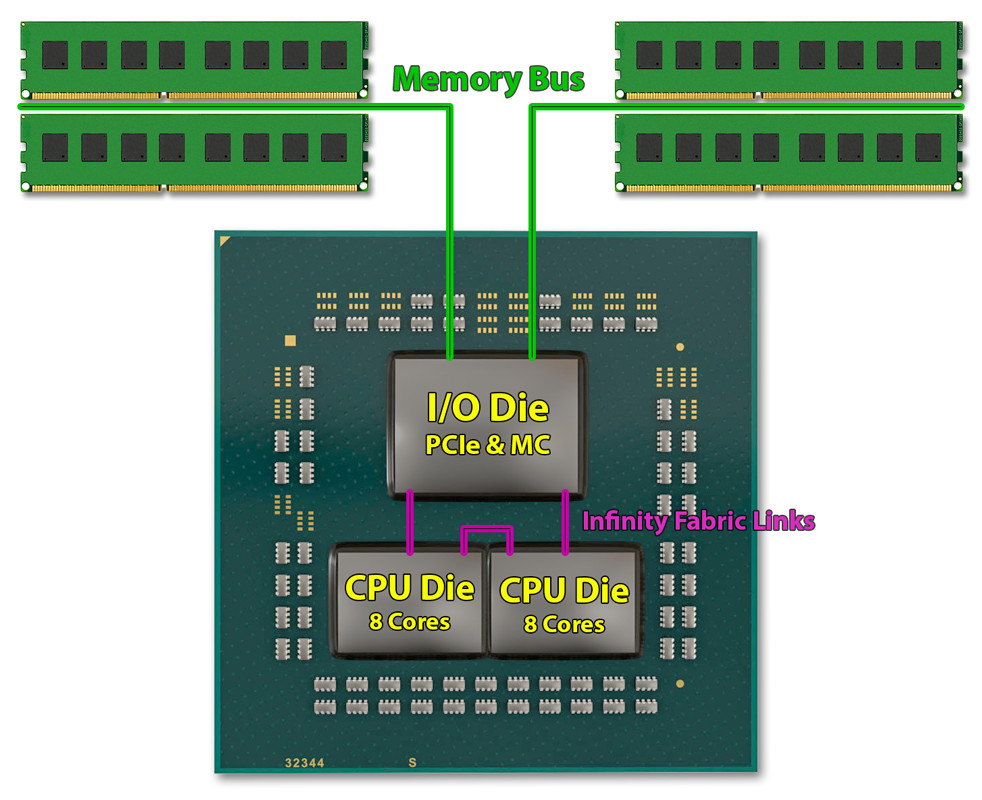

At CES 2019, AMD unveiled extra technical particulars and a prototype of a third era Ryzen socket AM4 processor. The firm confirmed that it’ll implement a multi-chip module (MCM) design even for his or her mainstream-desktop processor, during which it’ll use one or two 7 nm “Zen 2” CPU core chiplets, which discuss to a 14 nm I/O controller die over Infinity Fabric. The two greatest elements of the IO die are the PCI-Express root advanced, and the all-important dual-channel DDR4 reminiscence controller. We convey you by no means earlier than reported particulars of this reminiscence controller.

AMD has two huge causes to take the MCM route for even its mainstream desktop platform. The first is that it lets them mix-and-match silicon manufacturing applied sciences. AMD bean-counters reckon that it is extra economical to construct solely these elements on a shrunk 7 nanometer manufacturing course of, which might profit from the shrink; particularly the CPU cores. Other elements just like the reminiscence controller can proceed to be constructed on present 14 nm applied sciences, which by now are extremely mature (= cost-efficient). AMD can be competing with different corporations for its share of seven nanometer allocation at TSMC.

The 14 nm I/O controller die may, in concept, be sourced from GlobalFoundries to honor the wafer-supply settlement. The second huge purpose is the economics of downscaling. AMD is anticipated to extend CPU core counts past Eight and cramming 12-16 cores on a single 7 nm slab will make carving out cheaper SKUs by disabling cores pricey, as a result of AMD is not all the time harvesting dies with defective cores. These mid-range SKUs promote in increased volumes, and past some extent AMD is pressured to disable completely practical cores. It makes extra sense to construct 8-core or 6-core chiplets, and on SKUs with Eight cores or fewer, bodily deploy just one chiplet. This method AMD is maximizing its utilization of treasured 7 nm wafers.

The draw back of this strategy is the reminiscence controller is not bodily built-in with the processor cores. The third era Ryzen processor (and all different Zen 2 CPUs), therefore have an “integrated-discrete” reminiscence controller. The reminiscence controller is bodily positioned contained in the processor, however shouldn’t be on the identical piece of silicon because the CPU cores. AMD is not the primary to give you such a contraption. Intel’s 1st era Core “Clarkdale” processor took the same route, with CPU cores on a 32 nm die, and the reminiscence controller plus an built-in GPU on a separate 45 nm die.

Intel used its Quick Path Interconnect (QPI), which was cutting-edge on the time. AMD is tapping into Infinity Fabric, its newest high-bandwidth scalable interconnect that is closely carried out on “Zen” and “Vega” product traces. We have realized that with “Matisse,” AMD might be introducing a brand new model of Infinity Fabric that provides twice the bandwidth in comparison with the primary era, or as much as 100 GB/s. AMD wants this as a result of a single I/O controller die should now interface with as much as two 8-core CPU dies, and as much as 64 cores of their “EPYC” server line SKU.

Our resident Ryzen Memory Guru Yuri “1usmus” Bubliy took a very shut have a look at certainly one of these BIOS updates with AGESA 0.0.7.x and located a number of new controls and choices that might be unique to “Matisse,” and presumably the next-generation Ryzen Threadripper processors. AMD has modified the CBS part title from “Zen Common Options” to “Valhalla Common Options.” We have seen this codename on the net fairly a bit over the previous few days, related to “Zen…