“The hybrid approach (doing fixed function acceleration for a single node of the bounded volume hierarchy (BVH) tree and using a shader unit to schedule the processing) addresses the issues with solely hardware based and/or solely software based solutions. Flexibility is preserved since the shader unit can still control the overall calculation and can bypass the fixed function hardware where needed and still get the performance advantage of the fixed function hardware. In addition, by utilizing the texture processor infrastructure, large buffers for ray storage and BVH caching are eliminated that are typically required in a hardware raytracing solution as the existing vector general purpose register (VGPRs) and texture cache can be used in its place, which substantially saves area and complexity of the hardware solution.”

Essentially, AMD might be introducing what it calls a “fixed function ray intersection engine”, which is specialised {hardware} that solely handles BVH intersection (processing BVH calculations in a stream processor solely through a software program answer is not a fairly possibility, since execution divergence implies that quite a few error corrections are required, which makes the method time and resource-intensive). This fastened operate {hardware} (which is nothing like NVIDIA’s RT cores and is way easier) is added in parallel to the feel filter pipeline in GPU’s texture processor.

The thought is that the fixed-function raytracing {hardware} can now use the feel system’s already present reminiscence buffers as a substitute of getting to retailer raytracing-specific knowledge regionally, which provides to die space and chip complexity. Additionally, since there isn’t any software program to allocate assets and schedule work for the fixed-function {hardware}, pure {hardware} options require a further {hardware} scheduler just for RT-specific workloads, which AMD claims its implementation bypasses – the shader processor sends raytracing knowledge down the feel processing path for the fixed-function {hardware} to course of, saving much more die area that will be utilized in a “classical” {hardware} answer.

It’s fairly well-known that each Sony and Microsoft’s next-gen consoles will help raytracing, and might be AMD Navi-based in nature. It’s possible these customized chips have some extra of the particular mud from AMD’s RDNA structure (which is just sprinkled on shopper, PC-level Navi), and these particular parts actually pertain (even when not utterly) to each consoles’ raytracing capabilities. While the patent has been submitted a 12 months and a half in the past, that is the time to reap fruits from such a hybrid design; Some highlights on AMD’s method which were taken from the paper could be seen under, however in case you fancy a learn of the entire patent, comply with the supply hyperlink.

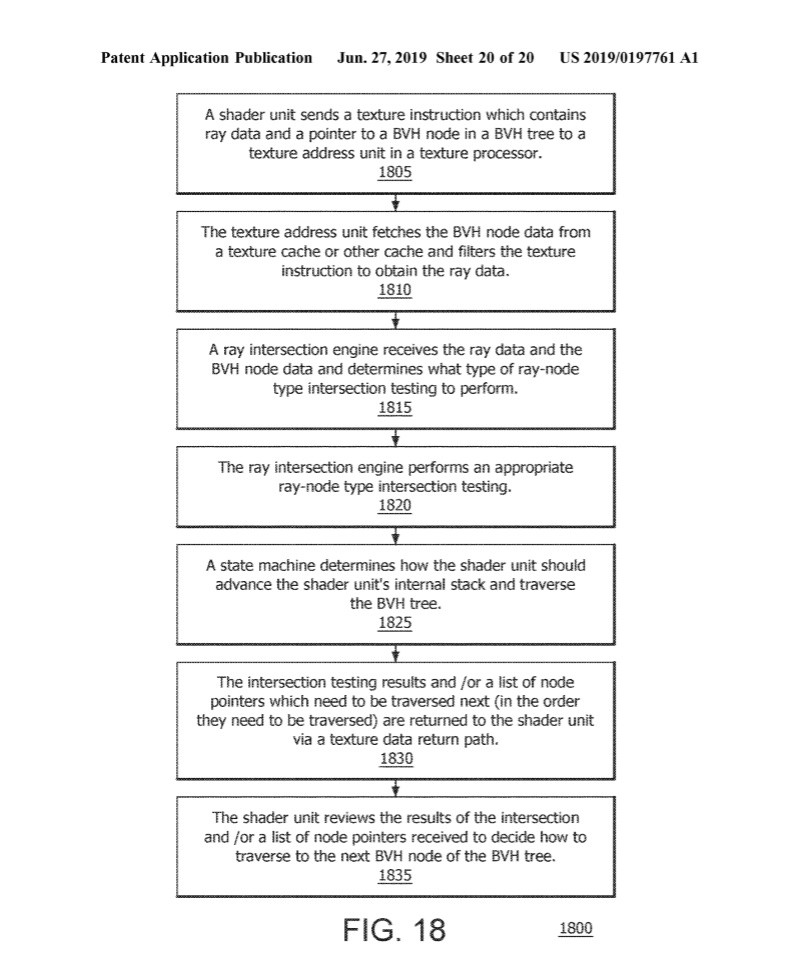

The system features a shader, texture processor (TP) and cache, that are interconnected. The TP features a texture deal with unit (TA), a texture cache processor (TCP), a filter pipeline unit and a ray intersection engine. The shader sends a texture instruction which incorporates ray knowledge and a pointer to a bounded quantity hierarchy (BVH) node to the TA. The TCP makes use of an deal with offered by the TA to fetch BVH node knowledge from the cache. The ray intersection engine performs ray-BVH node kind intersection testing utilizing the ray knowledge and the BVH node knowledge. The intersection testing outcomes and indications for BVH traversal are returned to the shader through a texture knowledge return path. The shader opinions the intersection outcomes and the indications to determine find out how to traverse to the following BVH node.

(…)

A texture processor based mostly ray tracing acceleration technique and system are…