AMD’s mic-drop second at Computex was the information of its carefully guarded “V-Cache” expertise, which might allow chip stacking on Ryzen CPUs.

PCWorld interviewed AMD’s Sam Naffziger about V-Cache. We boiled down that dialog right into a baker’s dozen of key issues you might want to know.

AMD

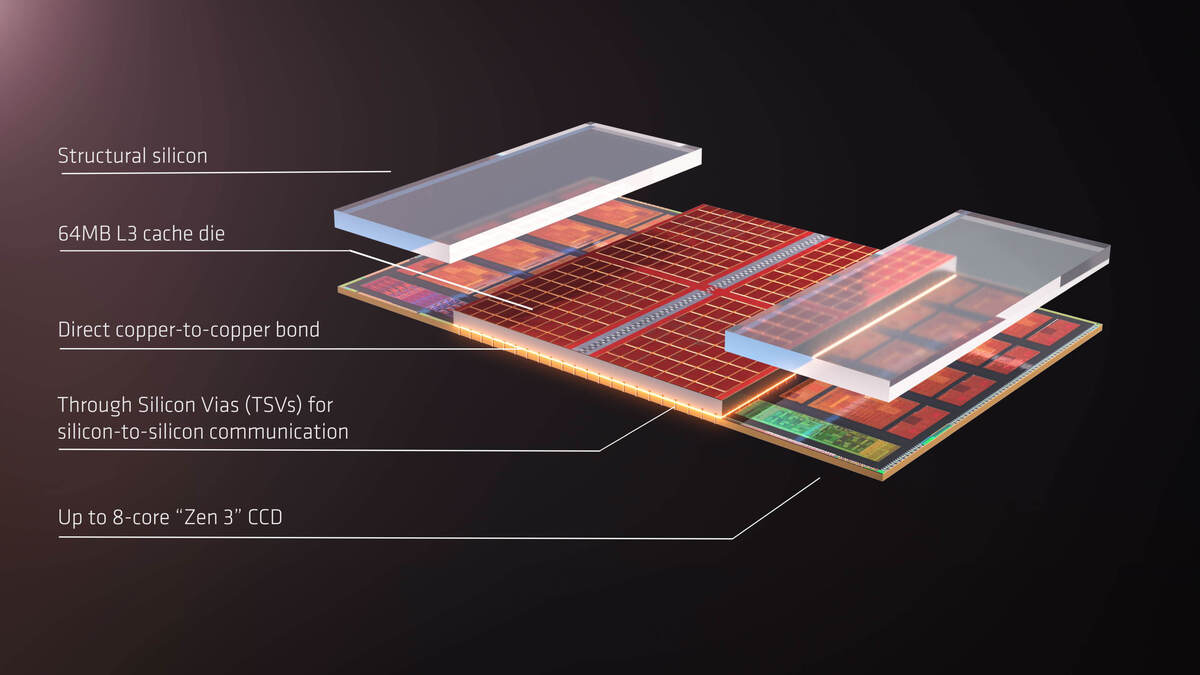

AMDThe V-Cache within the CPU above sits above the present CPU’s L3 cache. Additional silicon subsequent to it’s used to stiffen the die and convey warmth to the warmth spreader.

What is V-Cache?

V-Cache makes use of TSMC’s SoIC (System on Integrated Chips) chip-stacking expertise so as to add 64MB of SRAM L3 cache to the compute dies of present Zen 3-based Ryzen CPUs. That will mainly triple the quantity of cache to an insane 192MB of L3 for the 12-core and 16-core variations of AMD’s CPUs.

V-Cache will come to Zen 3-based Ryzen CPUs later this 12 months

There was a bit confusion as to which CPUs would get V-Cache, and when, as AMD CEO Lisa Su held up a prototype Ryzen with the expertise. The firm has since confirmed that sure, V-Cache will come to high-end, Zen 3-based Ryzen CPUs on the finish of the 12 months.

AMD

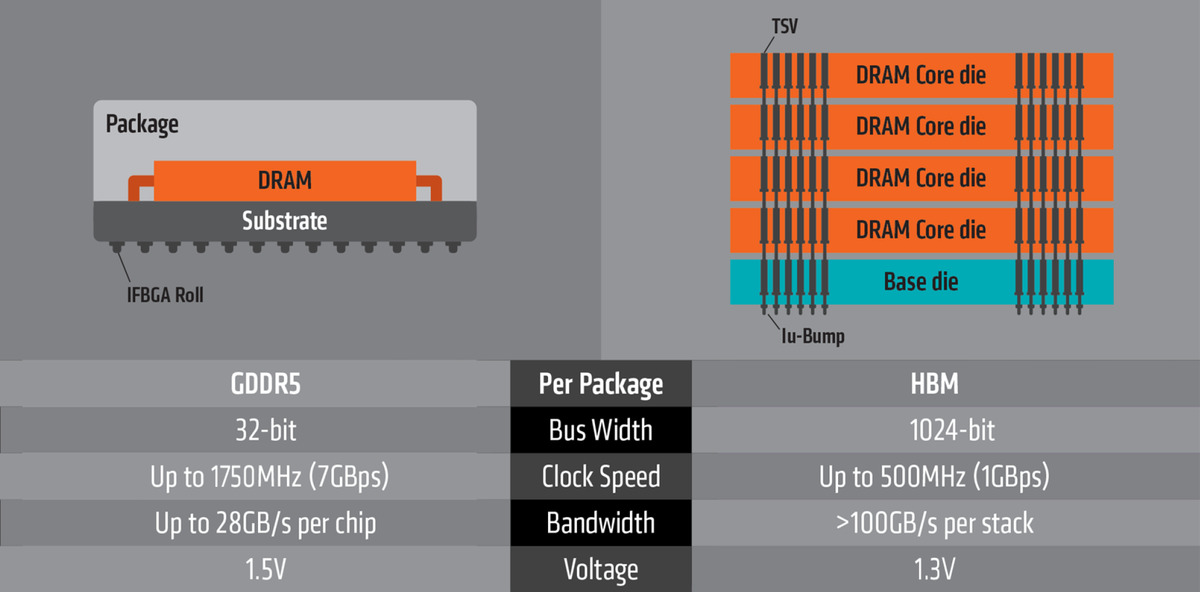

AMDAMD beforehand used TSV (Through-Silicon Via) expertise in its unique Vega GPU’s HBM reminiscence. As you’ll be able to see, it channels by means of the silicon itself to hook up with the following layer down.

How is V-Cache linked?

The particular person 64MB SRAM cache can be stacked on every compute die over the present L3 cache and be linked utilizing a expertise referred to as Through-Silicon Via, which connects stacked chips utilizing a tunneling system. This isn’t AMD’s first expertise with TSV: The unique Vega GPU with its HBM reminiscence additionally used TSV expertise.

Latency shouldn’t be a difficulty

One concern with the massive quantity of L3 is latency, or delay, because the CPU fetches directions or information from the cache. AMD’s Naffziger mentioned that shouldn’t be an issue with V-Cache, as a result of the TSV development gives a extra direct path to the cache.

How quick will V-Cache be?

AMD is touting a jaw-dropping 2TBps and past of bandwidth for V-Cache. That’s insanely quick. As a comparability, Intel’s 2013-era Core i7-4770R “Crystal Well” chip, which featured a formidable 128MB of eDRAM L4, supplied about 100GBps of bandwidth on the time.

Can you stack extra V-Cache on high of one another?

Although that won’t occur with the primary Ryzen chips with V-Cache, there’s nothing that may forestall the stacking of V-Cache.

![[Interview] ‘Bixby Will Be Your Go-To Starting Point for](https://loginby.com/itnews/wp-content/uploads/2026/04/1775675971_Interview-‘Bixby-Will-Be-Your-Go-To-Starting-Point-for-100x75.jpg)