Interposers. EMIB. Foveros. Die-to-die stacking. ODI. AIB. TSVs. All these phrases and acronyms have one overriding function – they’re all concerned in how two bits of silicon bodily join to one another. At the easy degree, two chips will be linked via the printed circuit board – that is low-cost however doesn’t permit for nice bandwidth. Above this easy implementation, there are a selection of the way to attach a number of chiplets collectively, and TSMC has quite a lot of these applied sciences. In order to unify all of the totally different names it provides to its variants of its 2.5D and 3D packaging, TSMC has launched its new overriding model: 3DFabric.

3DFabric is smart as a model to tie the dozen or so mixtures of packaging know-how that TSMC provides. Broadly talking, 3DFabric is break up into two segments: on one aspect are all of the ‘front-end’ chip stacking applied sciences, comparable to chip-on-wafer, whereas the opposite aspect is the ‘back-end’ packaging applied sciences comparable to InFO (Integrated Fan-Out) and CoWoS (Chip-On-Wafer-On-Substrate).

Even with this association of TSMC’s applied sciences, it nonetheless introduces lots of acronyms for customers not acquainted with packaging choices. Some of them aren’t at all times apparent both, comparable to RDL or LSI, particularly for these which might be used to Intel’s model names for the packaging applied sciences it has. Hopefully we are able to deconstruct what these phrases and evaluate them to choices at different foundries.

TSMC-SoIC: Front-End Chip Stacking

The front-end chip stacking applied sciences, comparable to chip-on-wafer and wafer-on-wafer, are collectively often called ‘SoIC’, or System of Integrated Chips. The purpose of those applied sciences is to stack bits of silicon on prime of one another with out utilizing the ‘bumps’ that we see on the back-end integration choices. Here, the SoIC designs are actually creating bonding interfaces such that silicon can sit on prime of silicon, as if it was a single piece of silicon to start with.

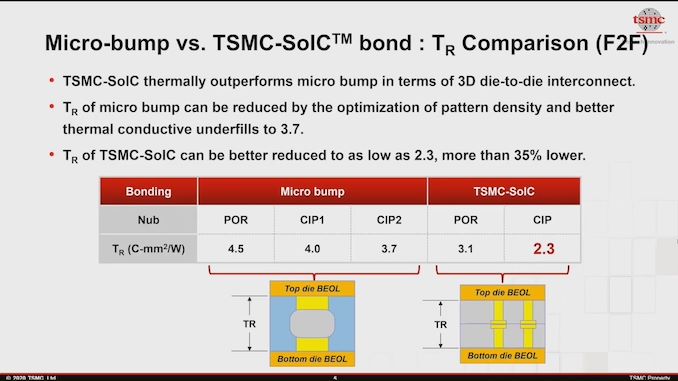

This is a technically extra advanced process, and the advantages usually lie in thermal efficiency:

This slide reveals that the thermal resistance of a face-to-face SoIC bond is as much as 35% decrease than a micro-bump connection, and as we transfer into the way forward for compute with a number of packaged chips, managing these interfaces for thermals goes to be robust. The draw back of those SoIC applied sciences nonetheless is that the stacked design needs to be co-designed with one another – microbump applied sciences, comparable to EMIB, are finished in such a manner that technically a spread of chips may very well be linked collectively. Using SoIC, as chip-on-wafer or wafer-on-wafer, the designs are fastened in from the beginning.

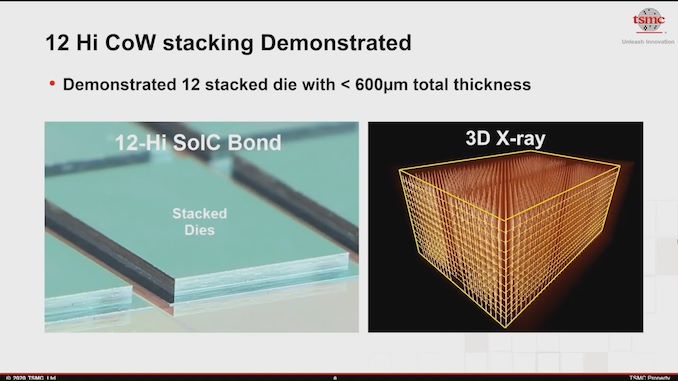

Nonetheless, TSMC is eager to advertise its SoIC chip stacking skills, with an illustration of a 12-layer stack as a part of the slide deck. You can learn our separate protection of this in our information article.

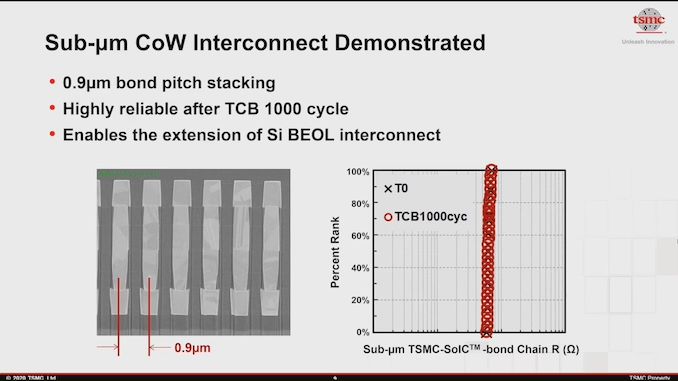

Naturally there may be concern about connecting two bits of silicon with out micro-bumps, comparable to density and reliability. TSMC states that they’ll show dependable 0.9 micron bond pitches in a really dependable format. If we evaluate that to the most effective bump pitch stacking that Intel has on its roadmap, the corporate is aiming for 10-micron bump pitches, which is an order of magnitude larger. In this case, for the chips the place it is smart, SoIC provides higher connectivity density and decrease energy-per-bit.

TSMC is planning to supply SoIC choices on its N7, N5, and N3 course of nodes, with the TSV pitches cutting down from 9 micron to 4.5 micron in that point. TSMC is anticipating a daily cadence to this launch schedule, with choices showing roughly 6-12 months after every respective node strikes into excessive quantity manufacturing.

TSMC Back-End Advanced Packaging

Competing towards EMIB and Foveros

The different aspect in…