High-performance computing chip designs have been pushing the ultra-high-end packaging applied sciences to their limits within the current years. An answer to the necessity for excessive bandwidth necessities within the trade has been the shifts in the direction of giant designs built-in into silicon interposers, instantly related to high-bandwidth-memory (HBM) stacks.

TSMC has been evolving their CoWoS-S packaging expertise over time, enabling designers to create larger and beefier designs with larger logic dies, and increasingly HBM stacks. One limitation for such advanced designs has been the reticle restrict of lithography instruments.

Recently, TSMC has been growing their interpose dimension limitation, going from 1.5x to 2x to even projected 3x reticle sizes with as much as eight HBM stacks for 2021 merchandise.

As a part of TSMC’s 2020 Technology Symposium, the corporate has now teased additional evolution of the expertise, projecting 4x reticle dimension interposers in 2023, housing a complete of as much as 12 HBM stacks.

Although by 2023 we’re positive to have a lot quicker HBM reminiscence, a 12-stack implementation with the presently quickest HBM2E Samsung Flashbolt 3200MT/s modules would characterize a minimum of 4.92TB/s of reminiscence bandwidth, which is multitudes quicker than even probably the most advanced designs right now.

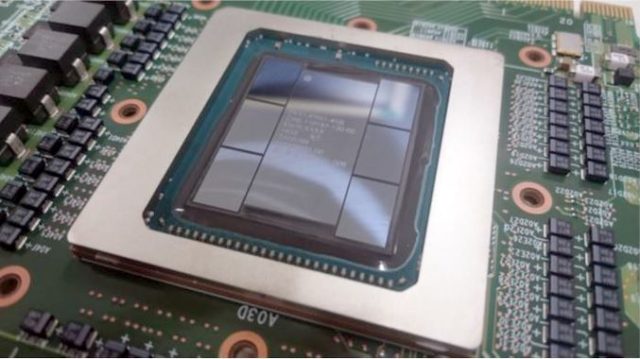

Carousel picture credit score: NEC SX-Aurora TSUBASA with 6 HBM2 Stacks

![[Video] Discover Your Ideal Bespoke AI Laundry Appliance](https://loginby.com/itnews/wp-content/uploads/2026/04/Video-Discover-Your-Ideal-Bespoke-AI-Laundry-Appliance-100x75.jpg)